Please select your location and preferred language where available.

先端技術トピックス

キオクシアで研究開発を進めている最新技術など参考になるトピックスをわかりやすく解説します。

-

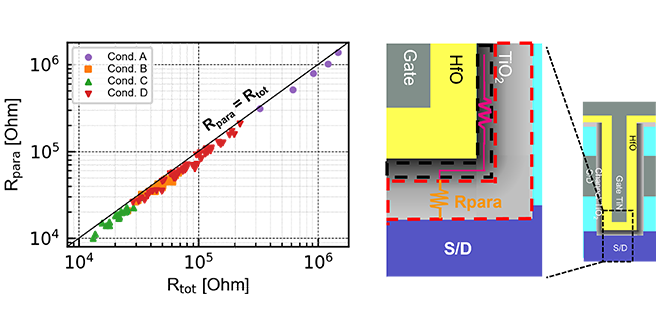

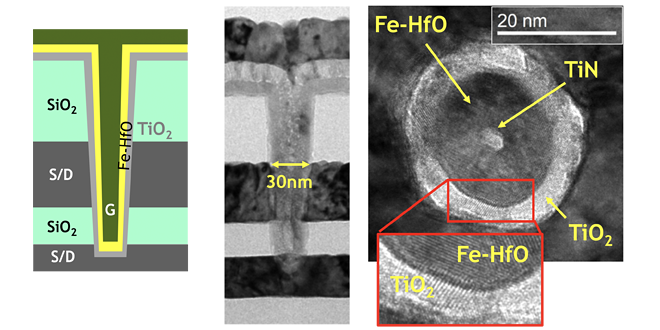

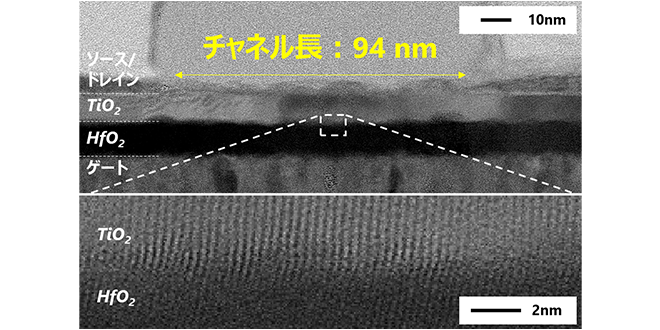

高速メモリの実現に向けて、チャネルオールアラウンド型強誘電体トランジスタ(CAA-TiO2 FeFET)の寄生抵抗発現メカニズムを調査し、抵抗低減指針を提案しました。CAA型構造特有の空乏化したTiO2チャネルが寄生抵抗の主成分であることを特定し、プロセス改善により寄生抵抗を98%低減することに成功しました。

-

垂直磁気異方性(PMA)ナノチューブ内の磁壁挙動を理論的に調査しました。スピン軌道トルク駆動の磁壁移動モデルを定式化し、磁壁シフト特性の迅速な定量予測を可能にしました。ナノチューブの径や磁気特性の調整によって磁壁速度を制御できる可能性を示し、デバイス設計に向けた重要な知見を提示しました。

-

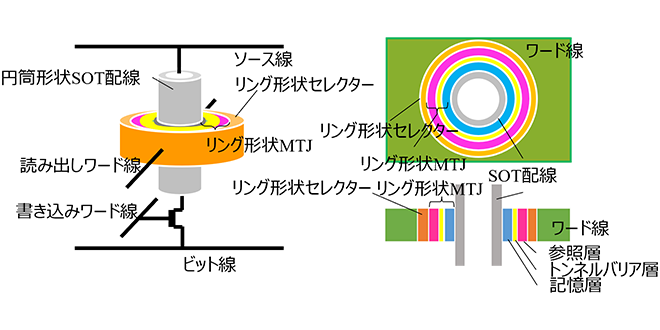

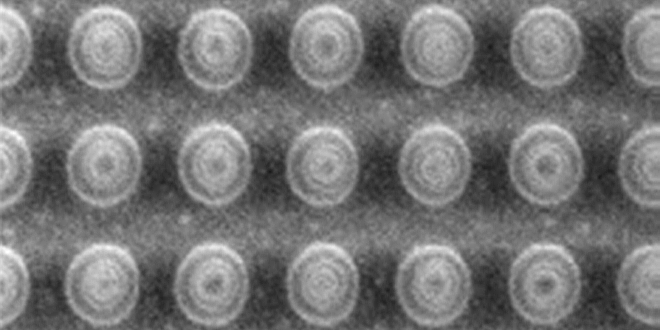

スピン軌道トルクを用いた磁気ランダムアクセスメモリ(SOT-MRAM)は、高速動作・低消費電力な新規メモリとして期待されています。従来のMRAMは、外部磁界擾乱耐性が課題でしたが、その解決策として、閉磁気回路で構成されるリング形状磁気トンネル接合(MTJ)素子を提案しました。リング形状MTJ素子では記憶層のSOT磁化反転は安定なコヒーレント磁化反転を示すことをマイクロマグネティック・シミュレーションで実証しました。

-

私たちは、微細な縦型ゲートオールアラウンド構造の酸化物半導体トランジスタにおいて、経時絶縁破壊耐性を改善し、高い信頼性を実証しました。この技術により、低消費電力かつ大容量化を実現する新しいメモリの実用化が期待されています。

-

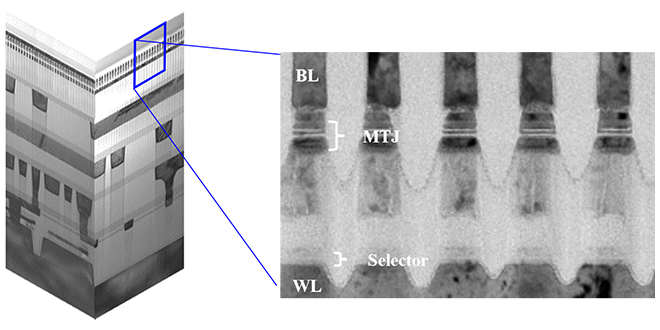

世界最小のセル面積0.001681 μm2を持つ64 GbitクロスポイントMRAM(磁気メモリ)を試作し、信頼性の高いセル動作を実証しました。この結果は、MRAMのSCM (Storage-Class Memory) 応用につながるものです。

-

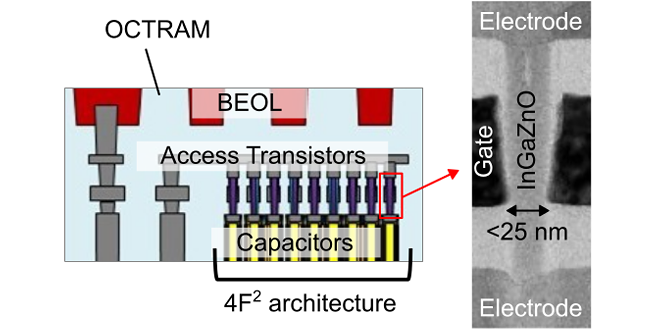

我々は南亜科技と共同で、酸化物半導体トランジスタを用いた新型DRAM「OCTRAM:Oxide-Semiconductor Channel Transistor DRAM」を試作しました。InGaZnOトランジスタの極低オフ電流という特徴により100秒を超える長リテンションを実証しました。これにより、従来のDRAMよりも低消費電力化が期待されます。

-

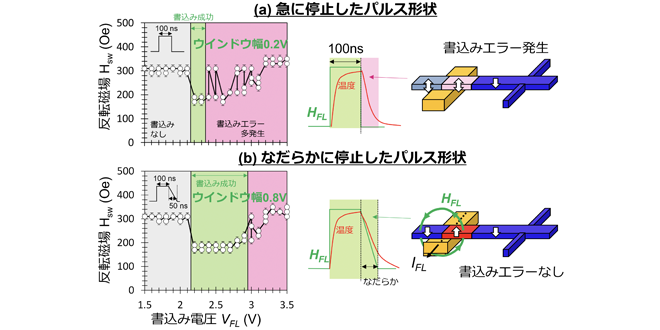

磁性体を使った新規ファイルメモリの候補の一つとして磁壁メモリを開発しています。磁性体への書込み方式として、誘導電流磁場書込み制御方式を新たに提案し検証しました。書込み時の電流パルス波形の電流降下速度を制御することで、電流磁場を印加しながらデバイス温度を低下させることに成功し、低エラーレートで安定な書込みを実現しました。これらの結果はSSDM 2024で発表しました。

-

近年のAI(人工知能)の急速な進歩により、大容量かつ高速で動作可能なメモリへの需要が高まっています。私たちは、世界で初めて300mmウェハ上でChannel-All-Around型の強誘電体トランジスタを試作し、微小なメモリセル(707nm2)で高い駆動電流(ΔIon>2μA)と安定したサイクル動作(>106cycle)を両立しました。

-

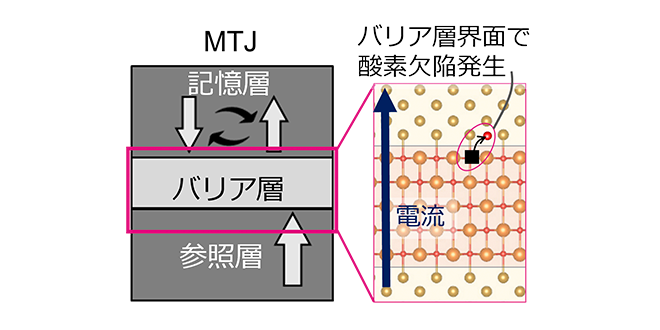

スピン注入磁化スイッチ型磁気メモリ(STT-MRAM)のメモリ素子(MTJ素子)の特性劣化の実測を行い、第一原理計算と時間発展モデルを用いることで、特性劣化のメカニズムと抑制方法の提案を行いました。本成果は、高密度で信頼性の高いSTT-MRAM開発において重要な結果であり、IRPS2024で発表されました。

-

高速、低電圧で駆動できるFeFETは次世代メモリの候補として注目されており、サイクル耐性改善が一つの課題となっています。我々は、FeFETのトラップ密度を調整するプロセスと動作方法を組み合わせて、107回の書込/消去ストレス印加後に2V以上のメモリウインドウを得ることに成功しました。

-

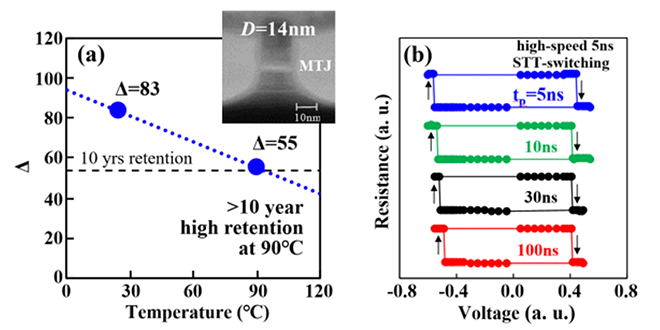

垂直磁化型磁気トンネル接合(MTJ)をメモリセルとして利用したスピン注入磁化スイッチ型磁気メモリ(STT-MRAM)は、大容量かつ低コストな高速不揮発性メモリの有望な候補として注目を集めています。我々は、複数の磁性層を組み合わせることで高速書き込み(5ns)と長時間情報保持(>10年)を両立する、14nm世代STT-MRAM向けMTJ技術(AccelHR-MTJ: Accelerated STT-Switching and High-Retention MTJ)を提案し、実証しました。この成果はIEDM2023で発表されました。

-

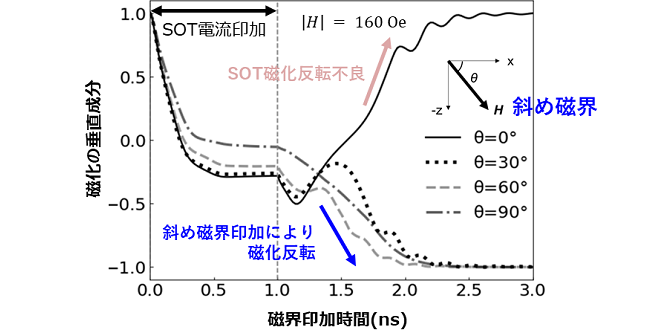

次世代磁気メモリ技術として注目されているスピン軌道トルク磁化反転において、垂直磁化磁性体ナノドットにおける印加磁界依存性を調べ、斜め磁界印加が垂直磁化スピン軌道トルク磁化反転を高速かつ安定にすることを明らかにしました。この成果は国際学会SSDM2023で発表されました。

-

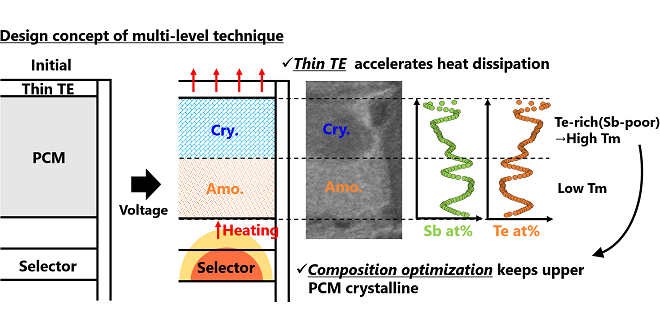

相変化メモリ(PCM)とセレクタ(Selector)を積層したセルを用いたクロスポイントメモリは、大容量で高速な不揮発性メモリとして広く研究開発されています。我々は、PCMの組成最適化と電極構造の最適化により、単一パルスで書き換え可能なセルの多値化技術を提案し実証しました。

-

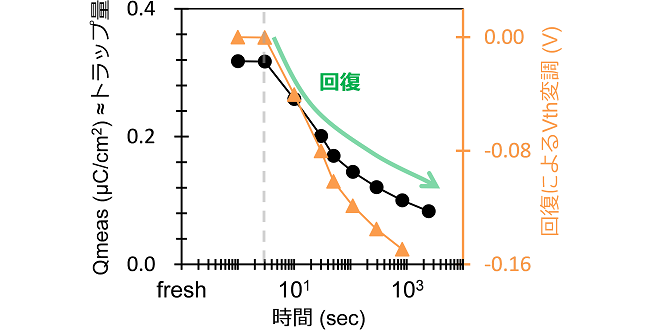

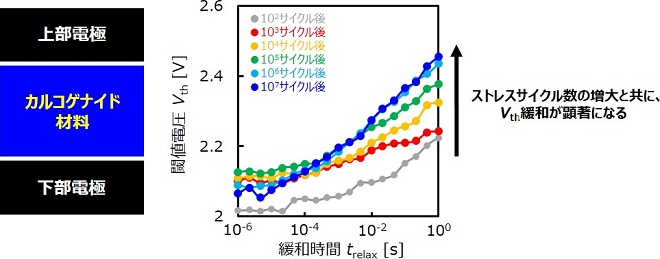

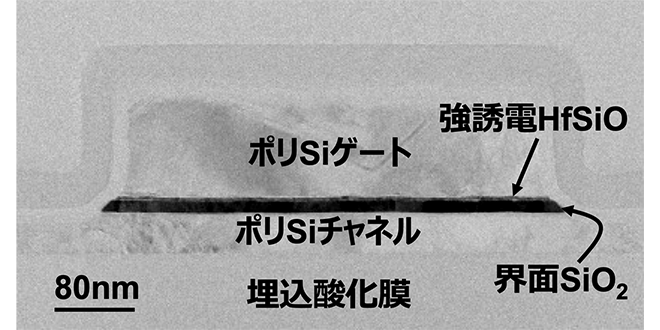

強誘電性HfO2を用いたFeFET (Ferroelectric FET) が次世代メモリの有力候補として注目されています。今回、私達は、書き込み/消去サイクルによって界面SiO2層に新たに生成したトラップサイトが、時間とともに消失することを明らかにしました。この回復現象は、データ保持中のしきい値電圧に無視できないレベルで影響しています。私達は、本成果を国際学会SSDM 2023で発表しました。

-

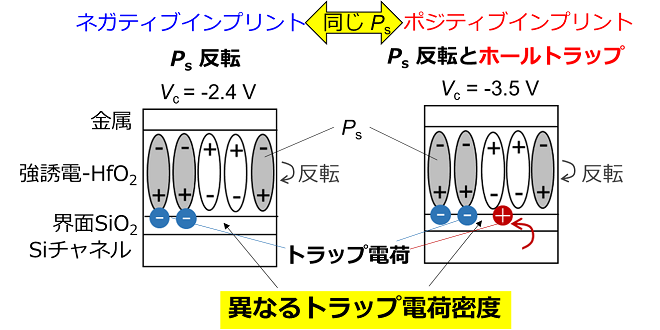

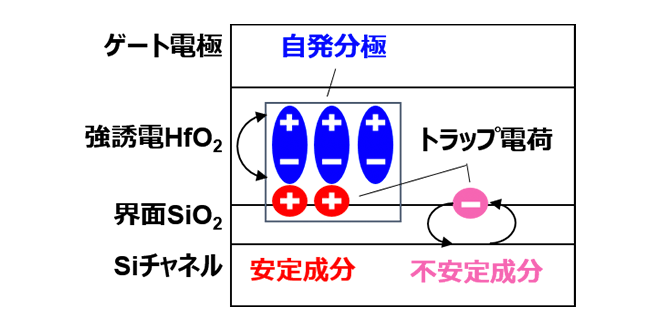

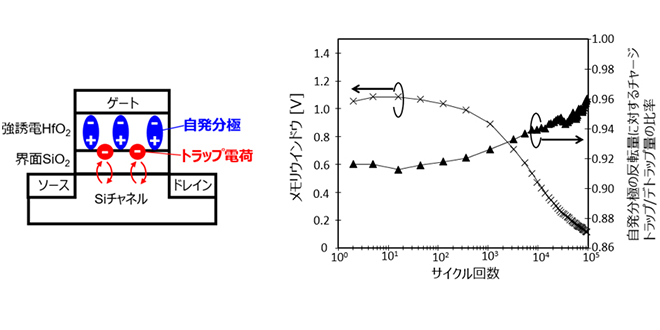

新規高速メモリの候補として注目を集めているHfO2-FeFETには、信頼性課題の一つであるインプリント*があります。これまで明らかにされていなかった自発分極、トラップ電荷とインプリントの関係を電荷成分解析により明らかにしました。この成果は国際学会SSDM2023で発表されました。

* 強誘電体の分極状態保持中に分極反転に必要な電圧(抗電圧Vc)が変化する現象

-

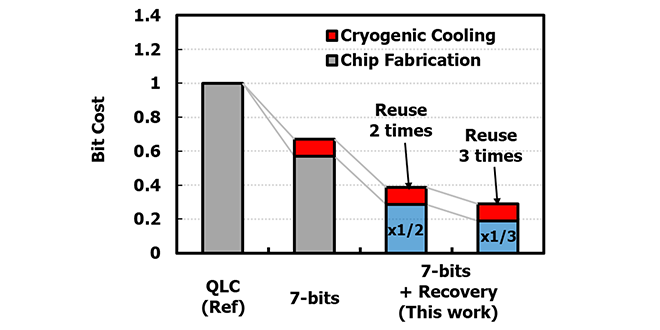

極低温で動作する7ビットセル・フラッシュメモリに適用する回復アニール技術を開発しました。本技術は、将来のビットコストのスケーリングやチップ寿命の延長など、持続可能な社会の実現に貢献することができます。

-

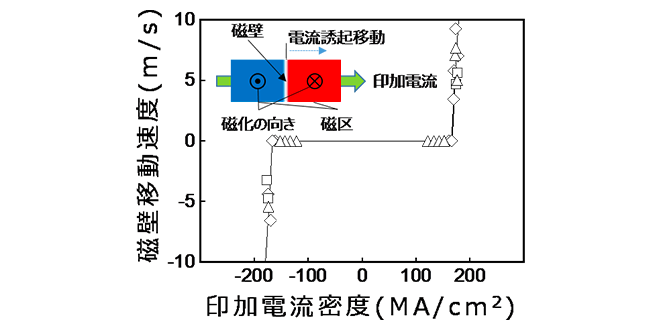

LSIの3次元集積化のキーテクノロジの一つである原子層堆積技術(アトミックレイヤーデポジション)を使って、磁壁移動メモリ(レーストラックメモリ[1])と呼ばれる3次元磁性素子に利用可能な物理現象(電流誘起磁壁移動)を示すCo強磁性薄膜を作製することに成功しました。この成果は国際会議INTERMAG 2023で発表されました[2]。

-

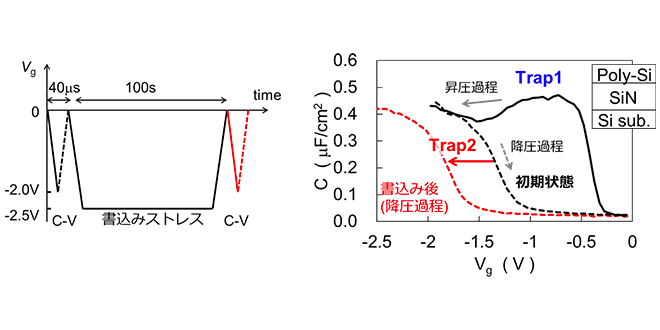

電荷蓄積メモリにおいて重要なSiN膜中のトラップ特性について、従来観測が困難であった短時間の特性評価手法を開発し、それによって正孔トラップ特性の包括的な描像を得ました。この成果は国際学会IRPS2023で発表されました。

-

次世代メモリの有力候補であるHfO2-FeFETにおいて、分極反転と電荷トラップの相互作用を明らかにし、アレイ動作中に意図せず情報が書き換わってしまう現象を強く抑制する動作手法を開発しました。この成果は国際学会IRPS2023で発表されました。

-

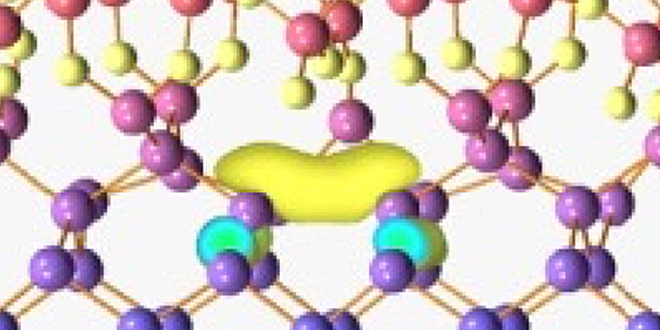

絶縁膜にHfO2を用い、電流経路にSiを用いた強誘電体MOSトランジスタはAI応用を含むメモリへの応用に広く研究開発されています。キオクシアはTiO2を電流経路に用いた強誘電体Field Effect Transistor(FET)を試作し、高速・低電圧動作および高サイクル耐性を実証しました。本成果は国際学会EDTM2023でBest Contributed Paper Awardを受賞しました。

-

エレクトロニクス技術における世界的な研究機関imecと共同で、次世代高密度メモリセルアレイの構成要素である選択素子の信頼性を検討しました。繰り返し動作に伴い生じる閾値変動をもたらすメカニズムを高精度な電気特性評価技術とモデリング技術を融合させて明らかにしました。この成果は国際学会IEDM2022で発表されました。

-

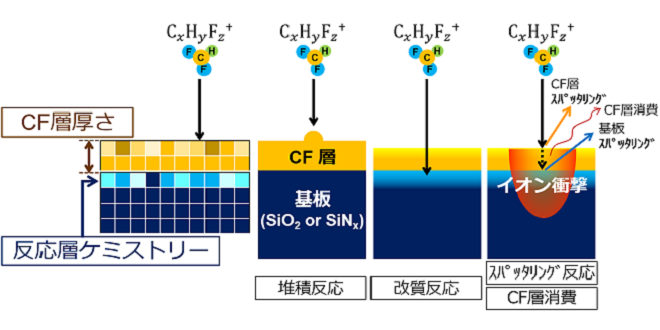

メモリデバイスの高積層化に伴い、アスペクト比の高い構造を高速にエッチングする技術が欠かせません。主要な役割を担うイオンが引き起こす表面反応をモデル化し、高速エッチングに適したイオン分子組成を予測するシミュレーション技術を開発しました。

-

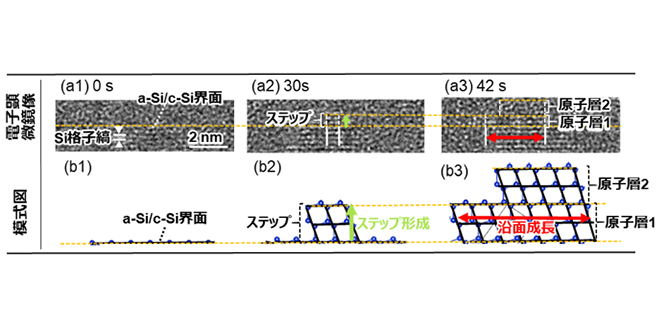

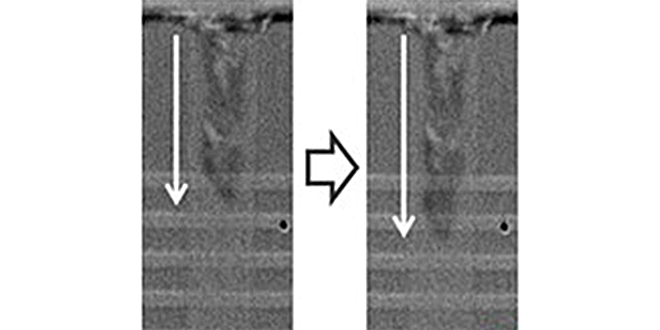

3次元LSIではポリシリコンにトランジスタを形成します。トランジスタの高性能化には欠陥のないポリシリコンを形成することが重要です。その形成プロセスを確立するために、従来の電子顕微鏡技術を改良し原子スケールかつリアルタイムの結晶粒の成長過程を観察しました。

-

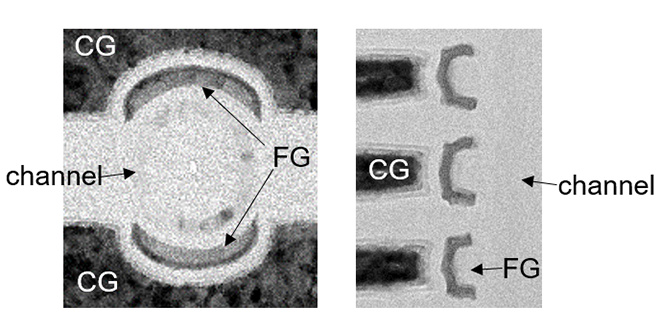

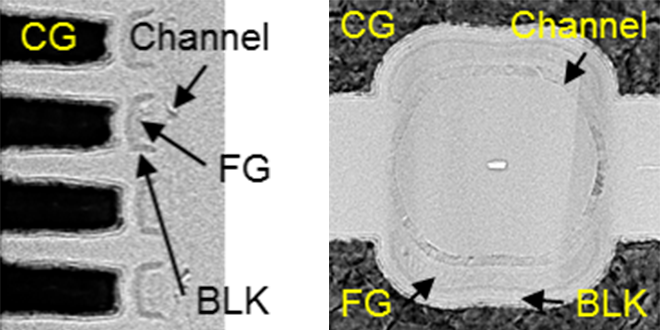

半円型セルの読出動作及び導電体電荷蓄積層(FG)形状の最適化により、多値動作に重要な広い書込/消去ウィンドウ、小さいしきい値電圧(Vth)分布幅、良好なデータ保持特性を実現しました。

-

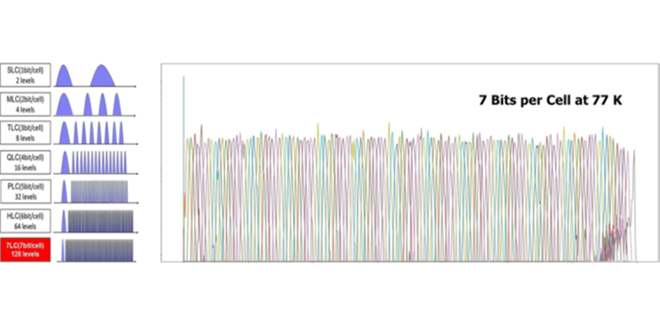

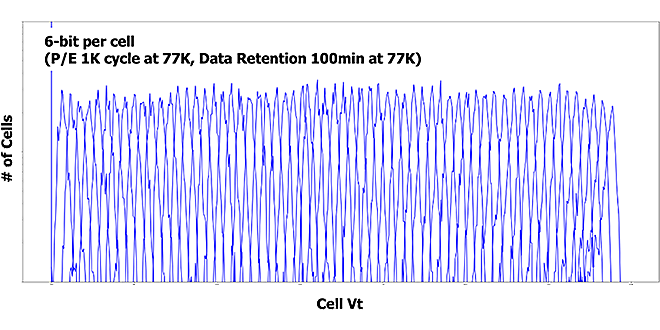

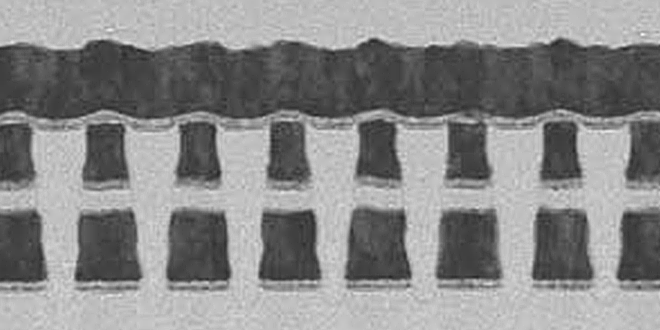

メモリセルの特性を向上できるシリコンプロセス技術と77Kの極低温動作とを組み合わせることにより、世界で初めて3次元フラッシュメモリの1セルあたり7ビット動作の実証に成功しました。

-

次世代メモリの有力候補である、HfO2-FeFETでは、書込みと消去を繰り返すと“0”と“1”の差が減少してしまう問題があります。これまで不明な点が多かったこのサイクル劣化の描像を、高速電荷中心解析により、明らかにしました。これにより、HfO2-FeFETメモリの実用化が進展することが期待できます。この成果は国際学会IEDM2021で発表されました。

-

近年では量子コンピューターの発展などを背景にコンピューターシステムの極低温動作などが求められ、そして低温による半導体素子の特性改善などが報告されています。そこで今回我々は3次元フラッシュメモリ(BiCS FLASH™)の極低温動作を調査し、ストレージ性能の向上を世界で初めて報告しました。

-

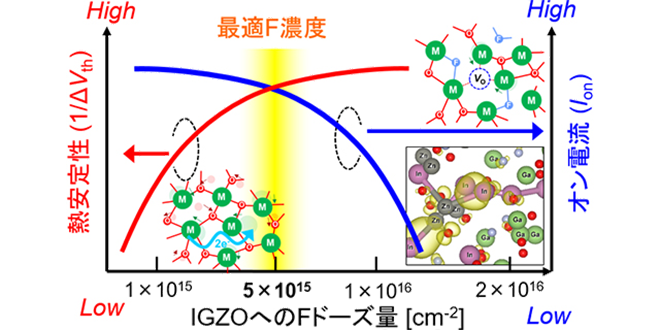

添加フッ素量を最適化したIGZO:Fを用いる事で、フォーミングガス熱処理耐性と高オン電流が両立した酸化物半導体FETを実現できることを示しました。これらの成果は、シリコンFETでは成しえない大容量・低遅延・超低消費電力なメモリ製品を実現する基盤技術の一つとなります。

-

低消費電力で集積度の高いAI(人工知能)向けインメモリコンピューティングの実現に向け、強誘電膜としてHfO₂を用いた強誘電メモリが近年注目を集めています。

-

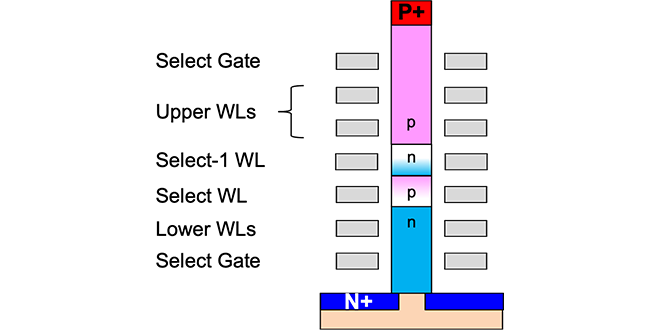

BiCS FLASH™はワード線の積層数を増やすことによって記録密度を向上させ、コストを下げることができます。高積層化してもメモリの読出し速度を維持するための一つの方法として、サイリスタ構造が提案されています。

-

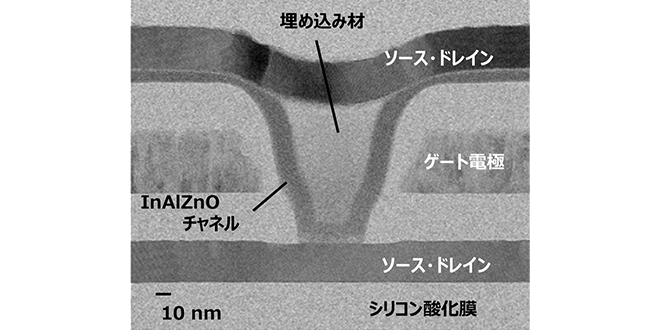

酸化物半導体トランジスタの課題の一つは、熱安定性の向上です。現在主流の酸化物半導体であるInGaZnO(IGZO)を用いるとメモリ素子製造過程で必要な高温熱処理によってトランジスタが正常に動作しなくなります。この課題に対し、私達は熱安定性の高い新規酸化物半導体材料としてInAlZnO(IAZO)を新たに提案しました。

-

我々はMILC(Metal-induced Lateral Crystallization)技術をSiチャネルの結晶化に適用することで、縦型のメモリホールにおいて、ニッケルシリサイドを介して非晶質シリコンからの単結晶形成を実現することができました。また、この技術を搭載した3次元フラッシュメモリセル素子で、ポリシリコンをチャネルに用いた従来素子と比べて、優れた電気特性を示しつつ、ばらつきも小さくなることを実証しました。

-

円型セルのゲート電極を分断して半円型にすることでセルサイズを縮小し、より少ないセル積層数で高いビット密度を実現するセル構造 を開発しました。

-

テラビット級の超大容量二端子メモリを実現するためには、メモリ素子の動作電流低減が課題です。キオクシアでは、マイクロアンペア以下の低電流動作が期待される新たな二端子メモリ「銀イオンメモリ」に注目し、開発を進めています。

-

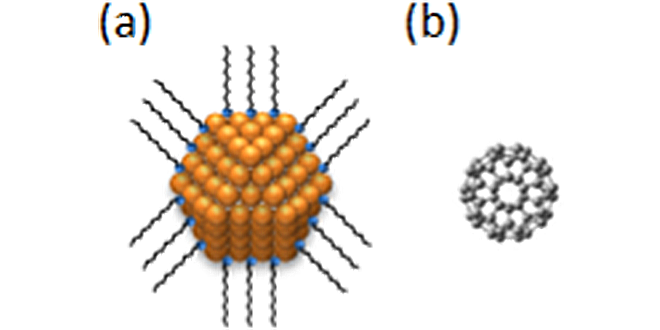

最先端の半導体プロセスを応用して、ナノ材料のサイズと同程度の隙間があるナノギャップを制御性良く一括形成し、ギャップ作成後にナノ材料を挿入することでナノ材料の電気特性を評価する手法を確立しました。

-

先端メモリ開発では、新たな材料や複雑な3次元デバイス構造の開発が必要とされており、開発を見通し良く、効率的に進展させるため、TCAD(Technology CAD)技術の活用が鍵となっています。

-

ファイルメモリの更なる大容量化・高集積化を実現するための新しいセル構造の提案や、新たな市場の創生も視野に入れた、各種の高速不揮発性メモリの技術開発などを行っています。

キオクシアの研究部門

豊かで持続的なデジタル社会の実現のため、メモリ技術の革新により、絶え間ない技術探索とその社会実装を目指します。

当社が世界に先駆けて開発した3次元フラッシュメモリ「BiCS FLASH™」の研究開発と量産化の橋渡しを行っています。