Please select your location and preferred language where available.

3次元フラッシュメモリ「BiCS FLASH™」

フラッシュメモリイノベーションの新時代

キオクシアは1987年にNAND型フラッシュメモリを発明し、現在、業界を代表するフラッシュメモリのサプライヤーの1つとして、技術力を高め続けています。2007年に発表した3次元フラッシュメモリ「BiCS FLASH™」は、革新的な垂直方向の積層と平面方向のスケーリングプロセスを導入し、面積あたりのメモリセルの数を大幅に増加させることが可能となりました。この技術により、キオクシアは技術革新に取り組む企業としての評価を高めてきました。その結果、絶え間なく高まるストレージ密度と性能向上へのニーズに応える、画期的なフラッシュメモリアーキテクチャが実現しました。

3次元フラッシュメモリ「BiCS FLASH™」 – お客様の用途に最適な設計

キオクシアの3次元フラッシュメモリ「BiCS FLASH™」は、高性能スマートフォンやPC、データセンターなど、データ中心のアプリケーションのニーズに応えるイノベーションです。高密度・高性能への要求に応えるため、BiCS FLASH™は世代ごとに改良や技術的進歩を積み重ねながら、特定の用途や投資計画にも配慮して設計されています。 キオクシアの3次元フラッシュメモリ製品をお選びいただくことで、急速に進化する現代のテクノロジーツールやアプリケーションのストレージおよび性能要件に応えることができます。

各世代のBiCS FLASH™の製品は、持続可能な技術ソリューションを世界に提供するというキオクシアのミッションを支えています。

多様なニーズに応えるBiCS FLASH™のノード展開

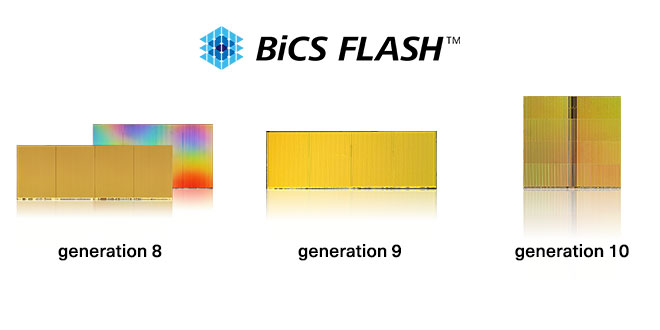

- ”gen.” は、BiCS FLASH™ の世代を示します。

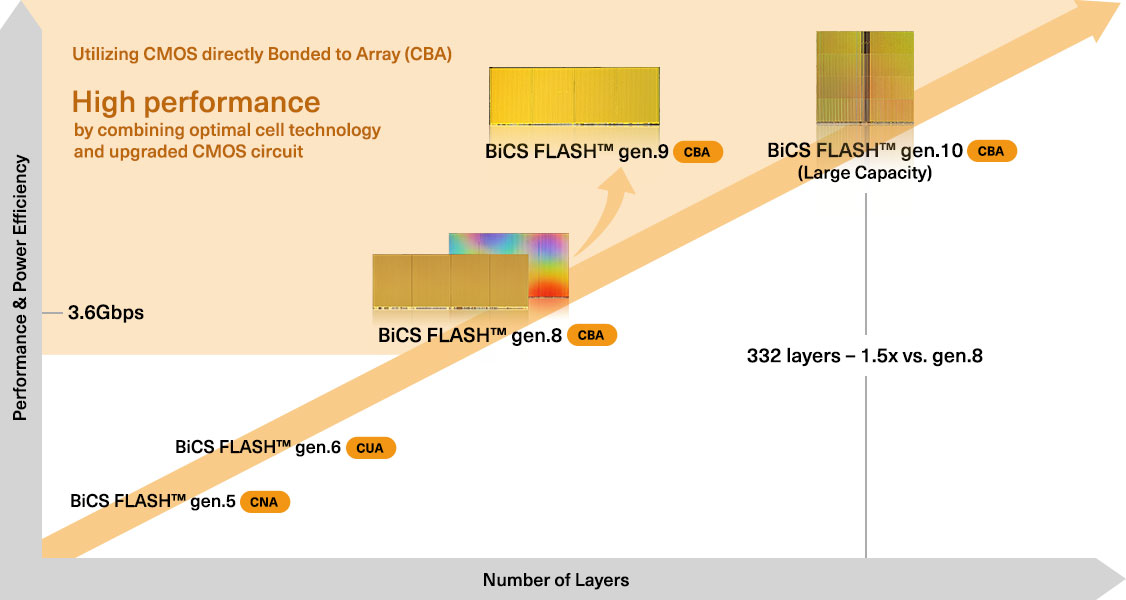

上の図に示されているように、キオクシアは密度、性能、電力効率などのさまざまな要件に対応するために設計された、複数世代のBiCS FLASH™製品を提供しています。キオクシアの二軸戦略、それは異なる市場ニーズに対応する2つの独立した3次元フラッシュメモリラインを開発するビジネス、および技術アプローチです。この戦略により、幅広い用途に高性能なフラッシュメモリを提供します。

BiCS FLASH™ 技術がもたらす多様なアプリケーションへのメリット

BiCS FLASH™ 第8世代 – 新しいアーキテクチャがもたらす圧倒的なメリット

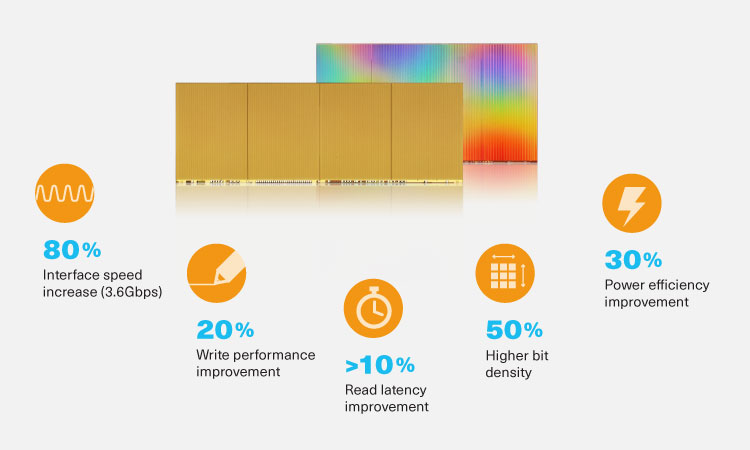

BiCS FLASH™ 第8世代では、フラッシュメモリの製造プロセスに新たな技術であるCMOS directly Bonded to Array(CBA)とOn Pitch Select Gate(OPS)を導入することで、大幅な性能の向上を実現しています。つまりCBA技術とOPS技術は、密度・性能・電力効率の向上を実現する製造と設計の技術です。

BiCS FLASH™ 第8世代は、データ集約型アプリケーションやAI技術の急速な拡大によってストレージ要件が高まっているお客様にとって、理想的な技術ソリューションです。

BiCS FLASH™ 第6世代からの改善点

次世代のBiCS FLASH™ 技術

BiCS FLASH™ 第9世代

優れた性能と電力効率

BiCS FLASH™ 第9世代の512Gbおよび1Tb TLC(Triple-Level Cell)は、低~中容量のストレージ領域において、高性能と優れた電力効率を求めるアプリケーションをサポートするよう設計されています。 第9世代のBiCS FLASH™ 製品は、既存のCBA技術とOPS技術を活用して、生産効率を向上させた最先端のフラッシュメモリソリューションを提供します。

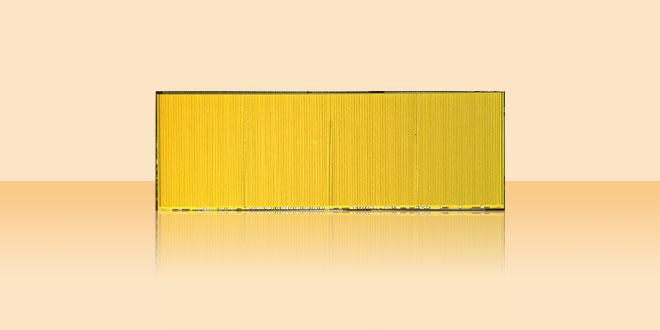

- 写真は 1Tb TLC製品です。

BiCS FLASH™ 第10世代

3次元フラッシュメモリの未来

BiCS FLASH™ 第10世代の製品は、第9世代と同様のCMOS技術を活用しながら、メモリの積層数を増やすことで、今後の大容量・高性能ソリューションの需要に対応します。業界を牽引する332層(第8世代比で1.5倍)で、キオクシアはフラッシュメモリのビット密度と電力効率においてさらなる進化を続けています。

大容量化への道を切り拓く革新的技術

BiCS FLASH™ 製品における大きな進化の背景には、いくつかの画期的なイノベーションがあります。密度、性能、電力効率の向上は、フラッシュメモリの設計および組み立て工程の進化によって実現されています。CBA技術、OPS技術、32枚積層技術が3次元フラッシュメモリの未来をどのように切り開いているかをご紹介します。

用途別に製品を見たい方

車載機器、小型高性能PC、クラウドサーバーやハイパースケールデータセンター用途などに高性能、大容量、低消費電力、低遅延、高信頼性で応える当社のメモリとストレージソリューションは、新しいアプリケーション開発を支え様々な技術・製品の潜在能力を引き出します。

ドキュメント

サポート情報

法人向け製品(メモリ・SSD・SDメモリカード)に関する技術的なご質問、各種資料請求、サンプル・ご購入などは、こちらからお問い合わせください。