Please select your location and preferred language where available.

フラッシュメモリの大容量化を実現する「多値化技術」とは

「多値化技術」はフラッシュメモリの大容量化を実現する主要技術の1つです。キオクシアは2001年に多値化技術を世界で初めてNAND型フラッシュメモリ製品に導入した1Gbit MLC NAND型フラッシュメモリを製品化しました。

フラッシュメモリの「1」「0」判定とデータの読み出し・書き込み動作

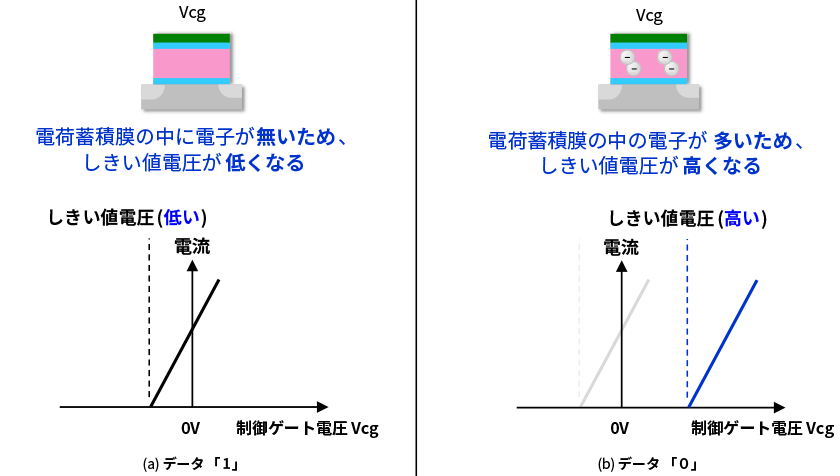

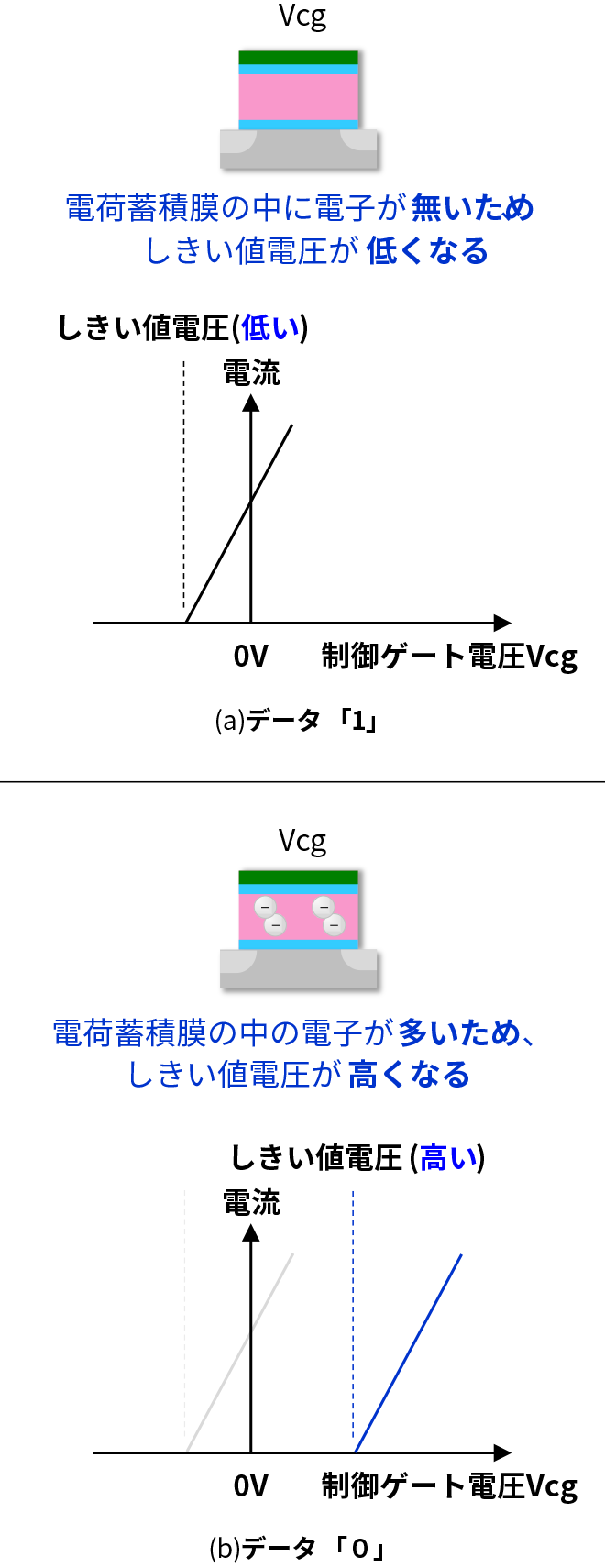

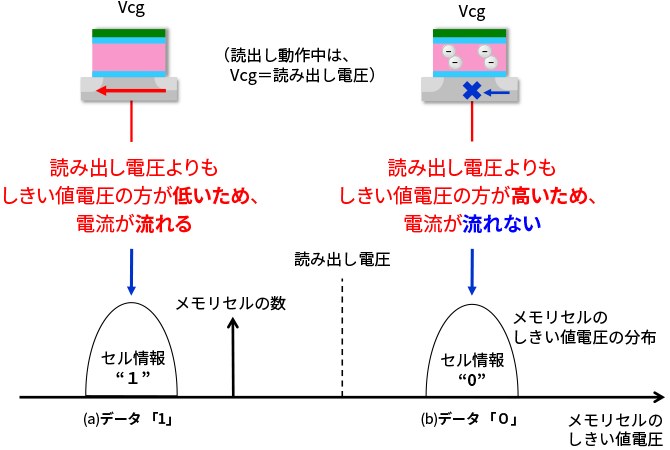

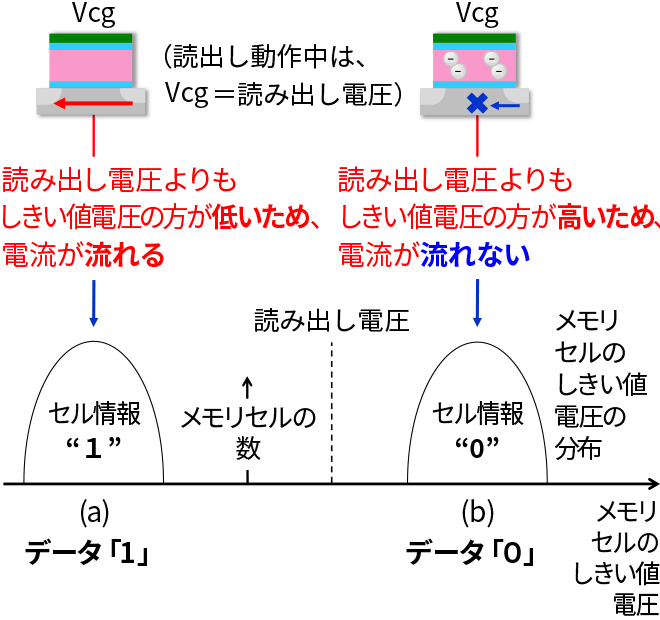

フラッシュメモリでは、メモリセルに電流が流れるかで「1」「0」を記憶しています。また、メモリセルの制御ゲートの電圧(Vcg)が高くなるほど電流が流れやすくなります。電流が流れる制御ゲートの電圧の下限を「しきい値電圧」と呼びます。

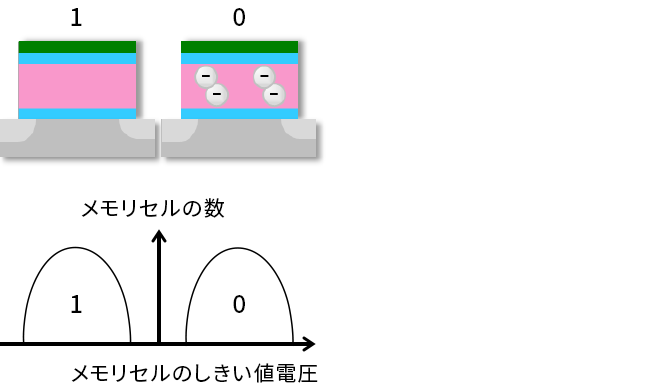

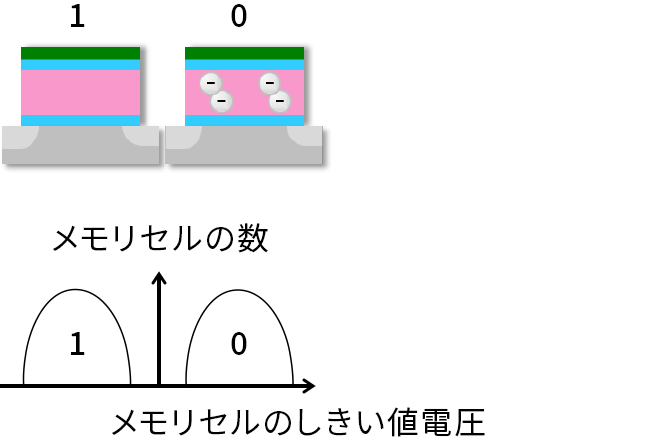

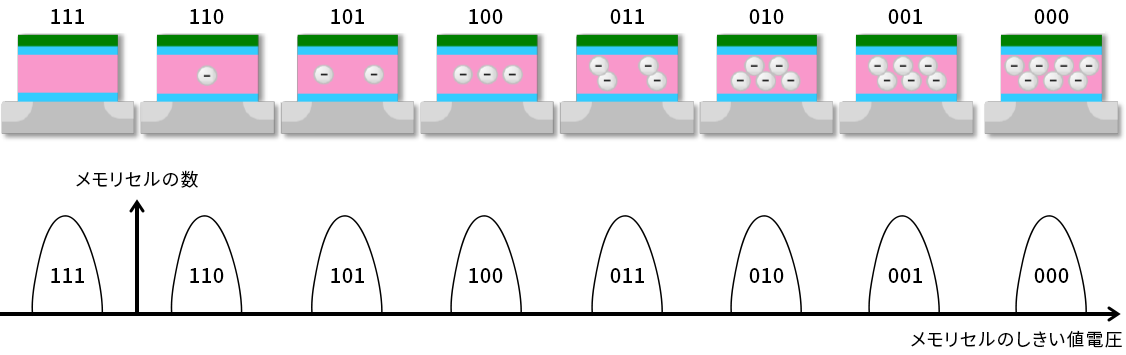

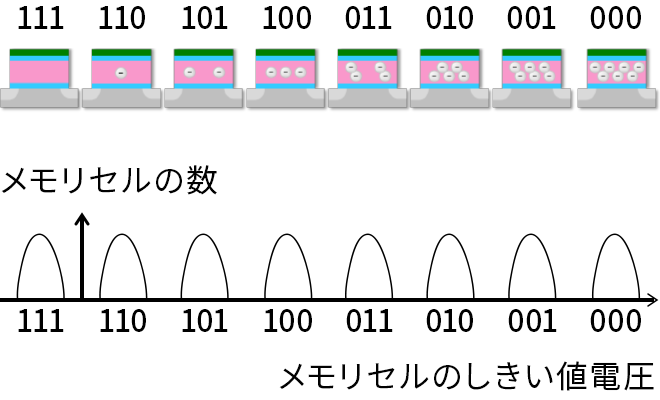

電荷蓄積膜の中の電子の数が少ない方が電流は流れやすくなります。このため、図1の(a)のメモリセルでは、電荷蓄積膜の中に電子が無いため、しきい値電圧が低くなります。一方、(b)のメモリセルでは、電荷蓄積膜の中に多くの電子があるため、しきい値電圧が高くなります。

電流が流れやすい状態、つまりしきい値電圧が低い状態はデータ「1」となります。また、電流が流れにくい状態、つまりしきい値電圧が高い状態はデータ「0」となります。実際のフラッシュメモリチップでは、非常に多くの数のメモリセルがあり、同じデータを持っていてもメモリセル毎にしきい値電圧の差が出てくるため、「1」のメモリセルのしきい値電圧は図2の(a)のように分布することになります。同様に、「0」のメモリセルのしきい値電圧は図2の(b)のように分布することになります。

読み出しの動作の時には、メモリセルの制御ゲートの電圧Vcgは、データ「1」のしきい値電圧分布とデータ「0」のしきい値電圧分布の間にある読み出し電圧に設定されます。この時には、データ「1」のメモリセルでは読み出し電圧よりもしきい値電圧の方が低いため電流が流れます。また、データ「0」のメモリセルでは読み出し電圧よりもしきい値電圧の方が高いため電流が流れません。

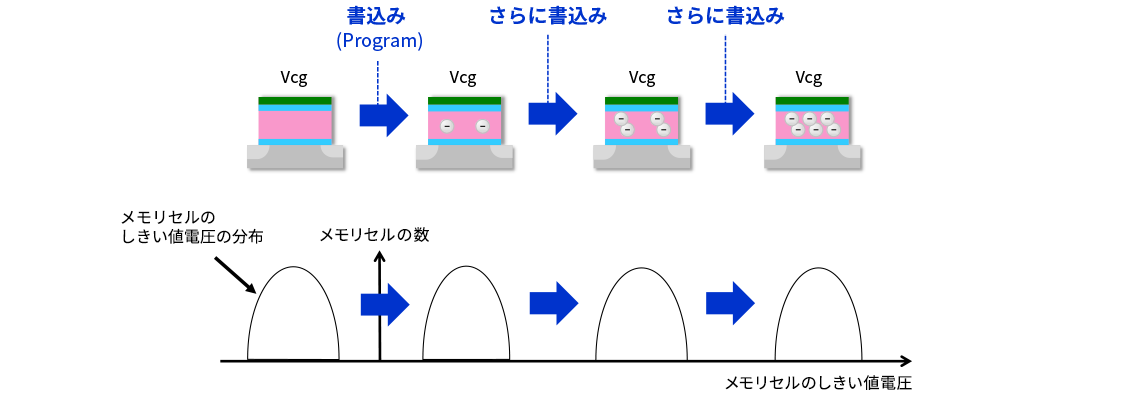

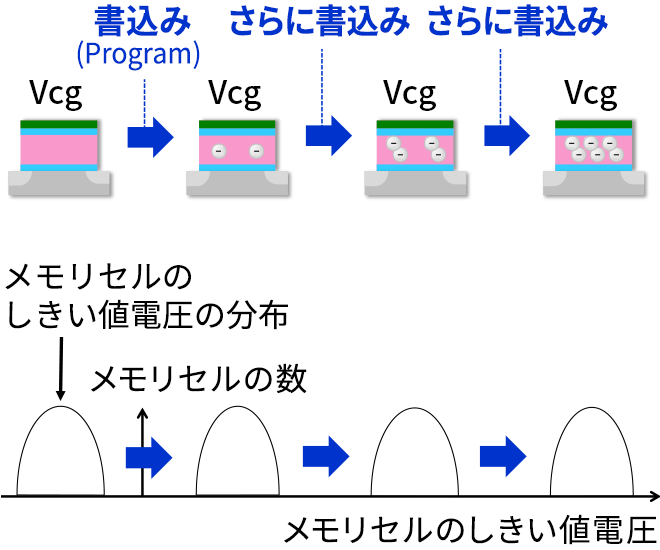

フラッシュメモリでは、書き込み動作によってメモリセルのしきい値電圧を変えることができます。図3に示しましたように、書き込みを繰り返すことにより、メモリセルの電荷蓄積膜の中の電子の数を増やしていくと、しきい値電圧も高くなっていきます。

多値化技術による大容量化のメカニズム

キオクシアでは、BiCS FLASH™における「多層化」以外の方法でもフラッシュメモリの大容量化を実現しています。そのひとつに「多値化技術」があります。

「多層化」では積み重ねることによって、単位面積あたりの「メモリセルの数自体を増やす」ことができます。一方、「多値化技術」では、「一つ一つのメモリセルに記憶できるデータの量」を増やすことができます。

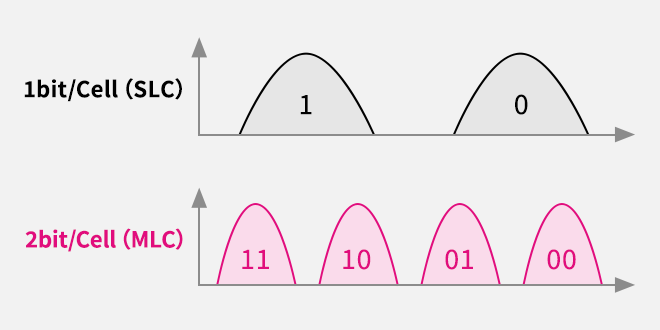

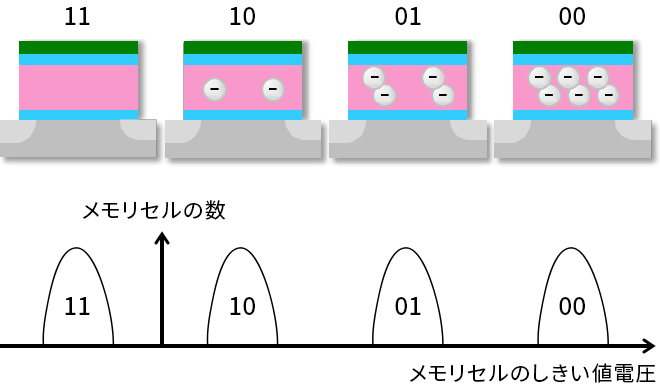

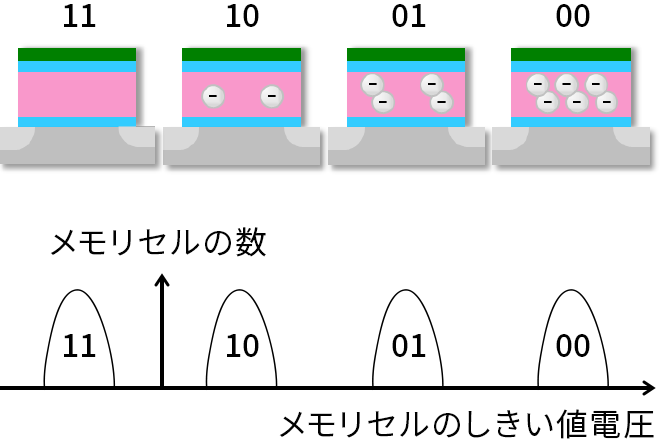

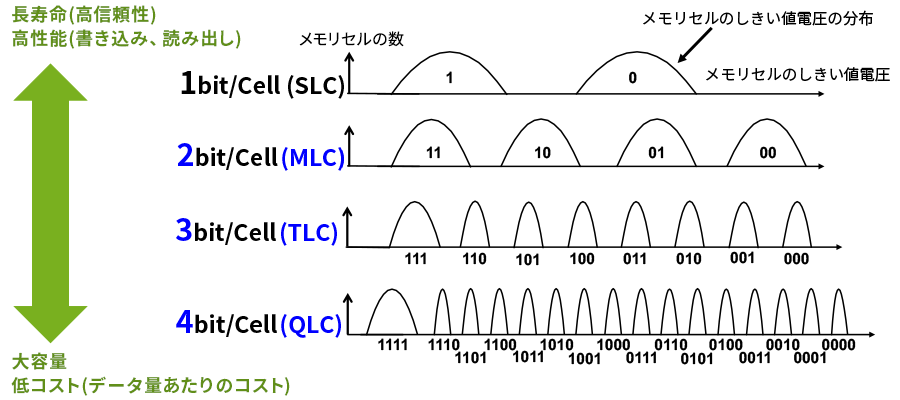

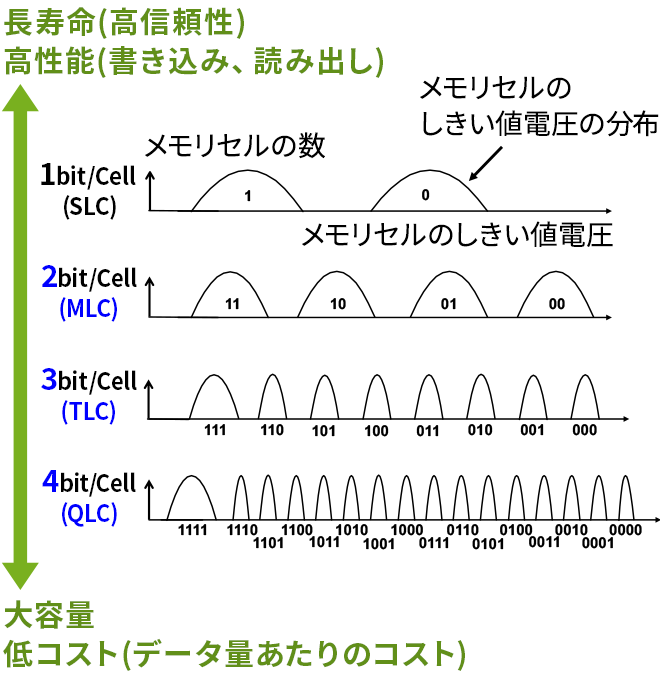

コンピュータで処理をするデータ量の単位は「ビット」と呼ばれ、「1ビット」というのは2進数で表現できる最小のデータ量を示します。1つのメモリセルに1ビットを記憶する従来のメモリセルでは、「1」と「0」の2つのパターンを記憶させていました。これが図4の「1bit/Cell(SLC)」のところに相当します。図3に示しましたように、メモリセルの電荷蓄積膜の電子数を細分化することにより、3個以上のしきい値電圧分布を作ることができます。例えば、4個のしきい値電圧分布を作ることができれば、図4の「2bit/Cell(MLC)」のところのように、それぞれのしきい値電圧分布を「0」と「1」の組み合わせで表現することができ、「11」「10」「01」「00」に相当する4種類のパターンを記憶できます。この場合には、1つのメモリセルで2ビット分のデータを記憶できることになります。同様に、8個のしきい値電圧分布を作ることができれば、図4の「3bit/Cell(TLC)」のところのように、8種類のパターンを記憶でき、1つのメモリセルで3ビット分のデータを記憶できるようになります。

略称の説明

SLC:Single Level Cell, MLC:Multi Level Cell, TLC:Triple Level Cell, QLC:Quad Level Cell

1bit/Cell (SLC) : 1つのメモリセルに1bitデータを記憶

2bit/Cell (MLC) : 1つのメモリセルに2bitデータを記憶

3bit/Cell (TLC) : 1つのメモリセルに3bitデータを記憶

図4 フラッシュメモリの多値化技術

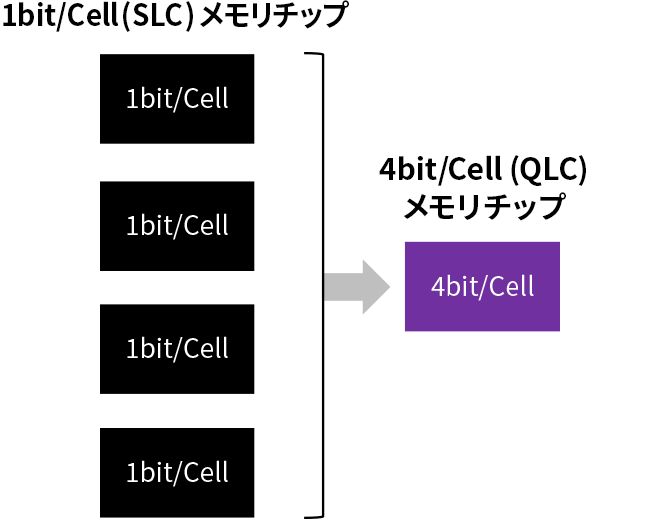

さらに、16個のしきい値電圧分布を作ることができれば、図5の「4bit/Cell(QLC)」のところのように、16種類のパターンを記憶でき、1つのセルで4ビット分のデータを記憶できるようになります。このように、1つのメモリセルのデータ量がNビットの場合には、しきい値電圧分布の数やパターンの種類は2のN乗個となります。

用途にあわせた多値化技術の使い分け

多値化技術により、フラッシュメモリのメモリセル1個あたりの記憶容量NビットのNの数が大きくなるほどフラッシュメモリの容量が大きくなるとともに、データ量当たりのコストを下げることができます。ただし、Nの数が大きくなるほどしきい値電圧分布を細くしなければなりません。このためには、書き込みをゆっくり行う必要があります。また、Nの数が大きくなるほどしきい値電圧の間隔が狭くなりますので、読み出しをゆっくり行うことが必要になり、さらにNの数が小さい場合と比べると、寿命が短くなります。つまり、Nが大きくなるほど容量やコストを重視する用途に向いており、Nが小さくなるほど性能や寿命の長さを重視する用途に向いています。このように、製品の用途に合わせて、フラッシュメモリのメモリセル1個あたりの記憶容量Nビットを使い分けることができるため、フラッシュメモリは非常に幅広い用途で使われています。

書き込みや読み出しをゆっくり行ったとしても、メモリセルのしきい値分布幅を小さくすることは容易ではありません。特に、図5のQLCのように、メモリセルのしきい値分布幅やしきい値分布の間隔を極端に小さくすることは技術的な難易度が高く、さらに、できる限り性能を高くして寿命を長くすることにもチャレンジする必要があります。このような目標に対して、回路・プロセス・製造などの幅広い分野の技術の集大成でQLCのような非常に高いレベルの多値化技術を実現することが出来ています。

略称の説明

SLC:Single Level Cell, MLC:Multi Level Cell, TLC:Triple Level Cell, QLC:Quad Level Cell

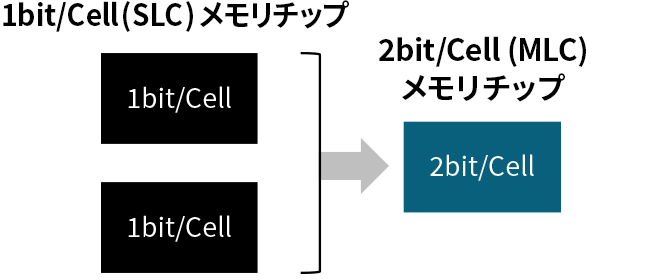

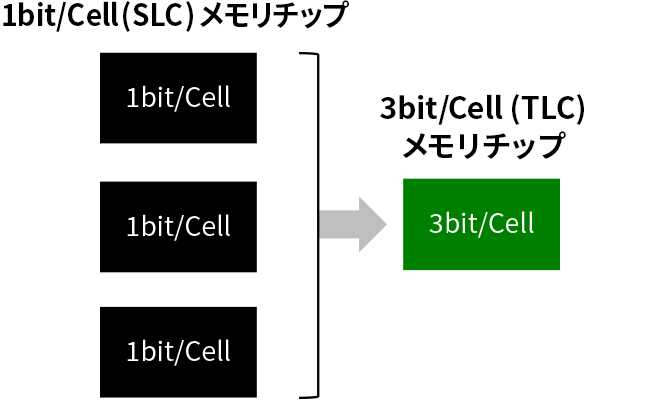

多値メモリチップによるメモリ搭載容量の増加

これまで説明してきました多値化技術を使いますと、複数のSLCメモリチップの容量を1つの多値メモリチップにより実現できるようになります。すると、図6に示しますように、例えば、これまでSLCメモリチップ2個の容量が必要だった製品をMLCメモリチップ1個で実現することができるようになります。同様に、SLCメモリチップ3個の容量が必要だった製品をTLCメモリチップ1個で実現できるようになり、さらに、SLCメモリチップ4個が必要だった製品をQLCメモリチップ1個で実現することができるようになります。

同じ容量を実現するためのメモリチップ数を減らすことができると、容量の上限を増やすことができる製品が出てきます。例えば、スマートフォンやメモリカードなどの非常に狭いスペースに色々な部品を入れる製品では、スペースにより搭載容量が決まる場合も多くなりますが、使えるスペースが同じ場合でも多値化技術を用いることにより搭載容量を倍以上に増やすことができるようになります。

これまで説明してきました多値化技術の開発はキオクシアが東芝時代から進めてきました。2001年には多値化技術を世界で初めてNAND型フラッシュメモリ製品に導入した1Gbit MLC NAND型フラッシュメモリを製品化しました。2007年にはQLC技術を世界で初めてNAND型フラッシュメモリに導入した16Gbit QLC NAND型フラッシュメモリを国際学会で発表しました。

- 図は多値化の仕組みを単純化したもので、実際の製品とは異なることがあります。