Please select your location and preferred language where available.

先端技術トピックス

キオクシアで研究開発を進めている最新技術など参考になるトピックスをわかりやすく解説します。

-

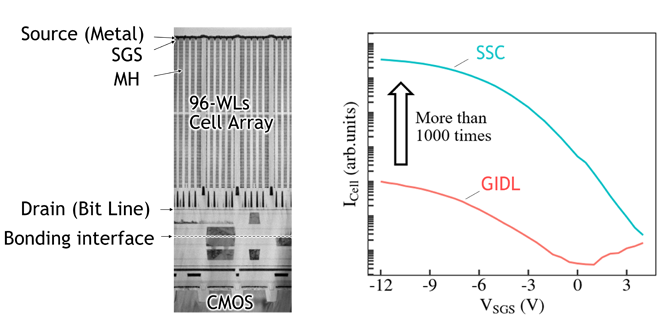

3次元フラッシュメモリは積層数の増加により、セルの消去動作に必要な正孔量が不足し、消去速度の低下が懸念されています。私たちは、消去速度を劇的に改善する新たな構造としてショットキーソース接合構造を考案し、試作品にてセルアレイ動作の検証を行いました。この成果はVLSI2025で発表されました。

-

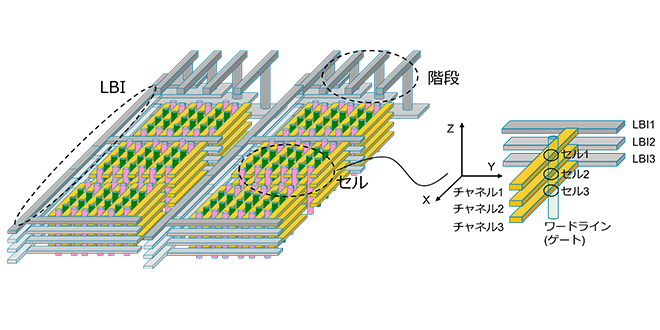

将来世代の3次元フラッシュメモリ候補として、新規水平チャネルフラッシュメモリ(Horizontal channel flash)の提案を行い、試作品にてセル基本動作および、10k cycleのProgram/Erase耐性を確認しました。この成果はIEDM2024で発表されました。

-

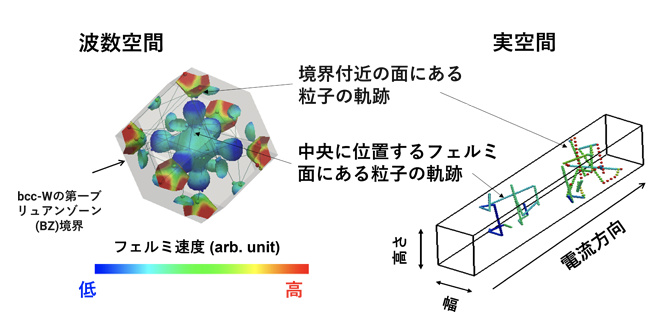

多結晶金属配線を縮小すると、電気抵抗が断面積の縮小以上に上昇する細線効果が発生します。また、抵抗上昇対策として金属を単結晶化すると、細線効果に結晶方位依存性が発現します。私たちはこの結晶方位依存性を予測するための計算技術の開発に成功しました。そして、この成果はSSDM2024で発表されました。

-

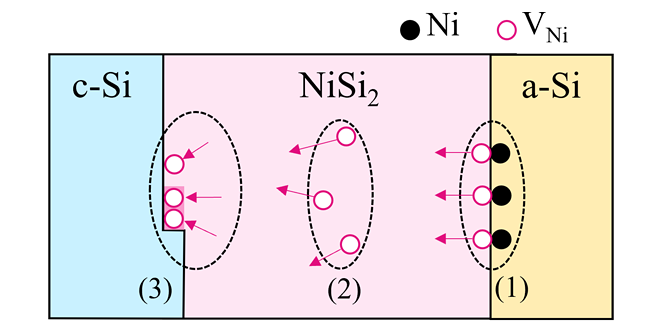

3次元フラッシュメモリの高積層化には、Siチャネルのメタルアシスト結晶化(MILC)が重要です。本研究では第一原理計算を用いることで、原子スケールでのMILCのメカニズムを理論的に明らかにし、その成果を国際学会SISPAD 2024で発表しました。

-

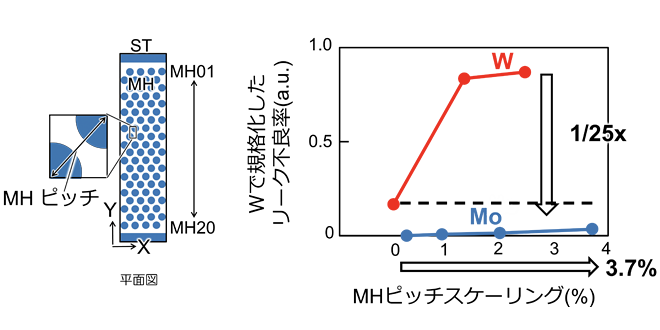

我々は、将来の3次元フラッシュメモリ向けに、最先端のフッ素フリー ワードライン (WL) モリブデン (Mo) プロセスを確立しました。MoをWLに適用することで、従来のタングステンに対してRC遅延を少なく、且つ、リーク不良率が低い状態で、垂直方向と水平方向の両方でセルの微細化を加速することができます。この成果はVLSI 2024で発表されました。

-

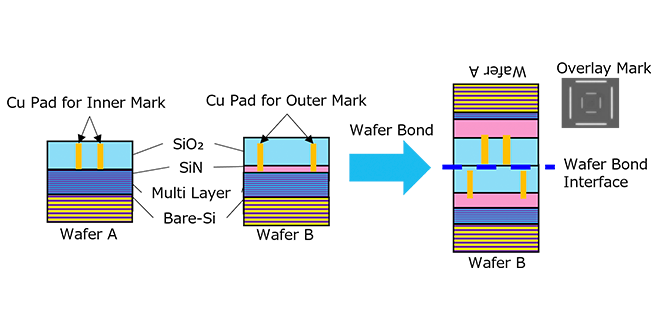

私たちは新規開発したIR光を用いた重ね合わせ検査装置を使用し、貼合重ね合わせの精度向上のための重ね合わせ精度制御技術の検証を行いました。IR光を用いた重ね合わせ測定器の検証は、シリコン研磨後の従来の重ね合わせ検査機と比較することで行いました。その結果、IR光を用いた貼合後の重ね合わせ結果とシリコン研磨後の結果に良い相関性がみられることを明らかにしました。

-

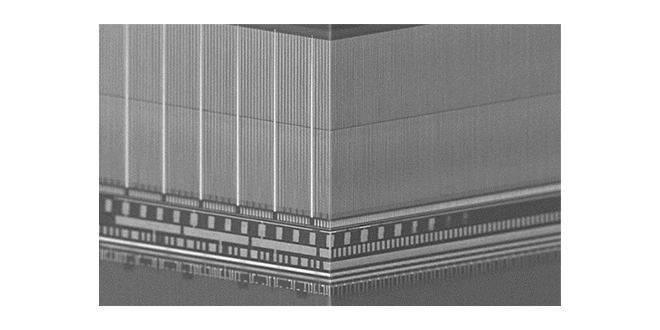

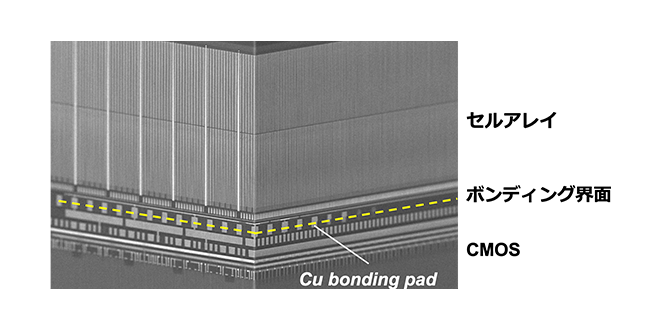

BiCS FLASH™ 第8世代では、1Tb TLCの製品においてデータ読出し時間40μs、データ書込み速度205MB/s、インターフェース速度3.2Gbpsの高速メモリ動作と18.3Gb/mm2の高メモリ密度を実現しています。高性能動作・高メモリ密度化に向け適用したCBA(CMOS directly Bonded to Array)とOPS(On Pitch SGD)の2つの新技術について紹介します。

-

3次元フラッシュメモリの性能向上、コスト削減を達成するため、Cu direct bondingプロセスを基盤としたCMOS directly bonded to array(CBA)技術を開発し、BiCS FLASH™ generation 8に適用しました。

-

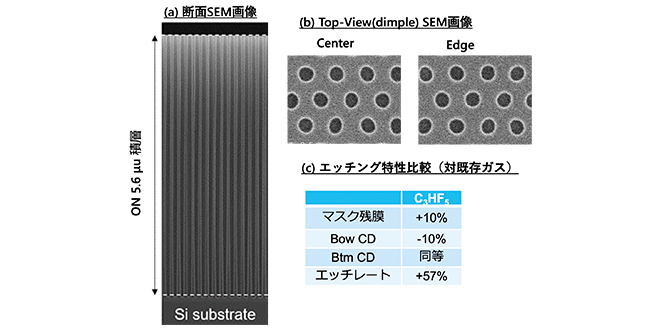

3次元フラッシュメモリのメモリホール加工では、高精度な形状制御性に加え高い生産性が求められています。本稿ではこれらの要求を実現する、環境にも配慮した新しいC3HF5ガスを用いたドライエッチング技術についてご紹介します。この成果は国際学会DPS2023で発表しました。

-

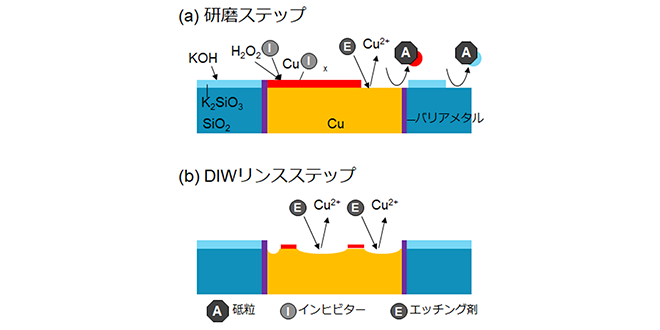

3次元フラッシュメモリの新技術であるCBA(CMOS directly Bonded to Array)プロセスにおけるCu貼合パッドのディッシング低減を検討しました。CMP工程中のケミカルエッチングを抑制することでディッシングを低減し、歩留を向上できることを明らかにしました。この成果は国際学会ICPT 2023で発表されました。

-

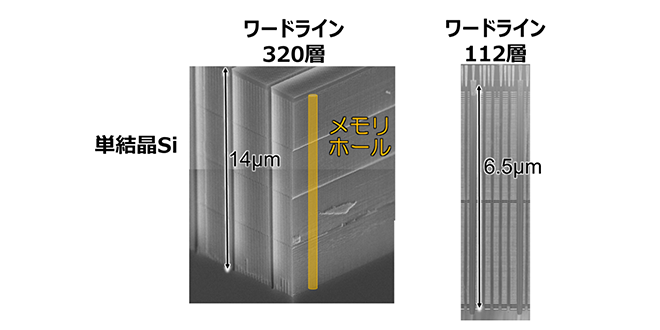

メタルアシスト材料を用いたSiチャネル単結晶化技術を3次元フラッシュメモリへ適用し、世界で初めてセルアレイ動作を実現しました。本技術を用いることで、従来の多結晶Siチャネルに対して、チャネル中の粒界密度が低減し、その結果チャネル中のトラップ密度が低減することで、チャネル抵抗の低減、ランダムテレグラフノイズ(RTN)の低減、QLC (quadruple level cell) 動作時のセル信頼性改善を実証しました。

-

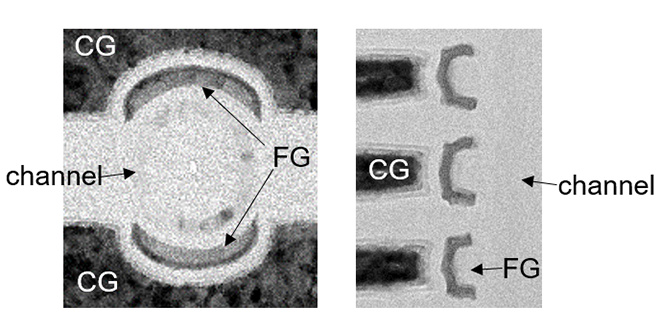

半円型セルの読出動作及び導電体電荷蓄積層(FG)形状の最適化により、多値動作に重要な広い書込/消去ウィンドウ、小さいしきい値電圧(Vth)分布幅、良好なデータ保持特性を実現しました。

-

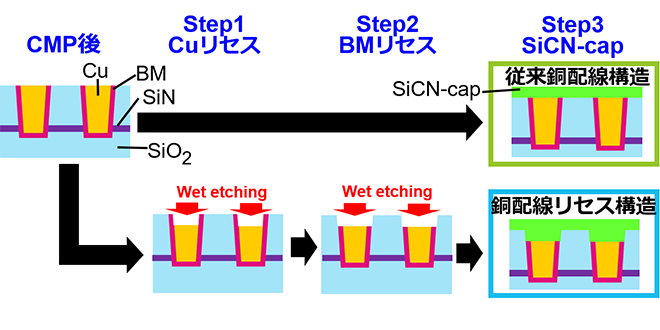

3次元フラッシュメモリの高電圧回路微細配線に銅配線を用いるために、高信頼性銅配線技術が求められています。銅配線リセス構造を開発し、銅配線間絶縁信頼性が向上することを示すことができました。

-

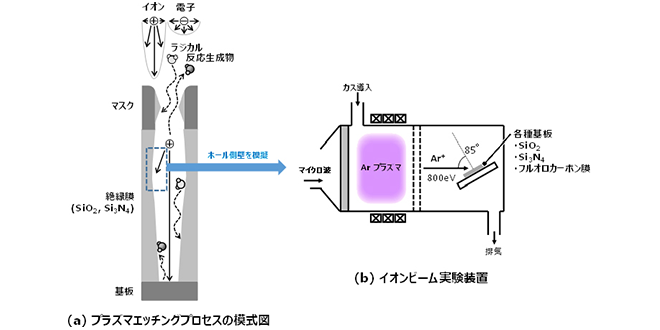

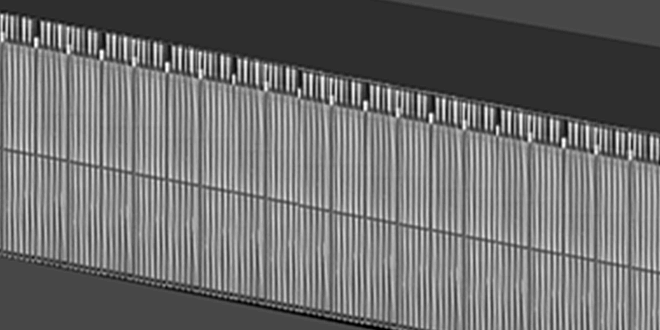

次世代BiCS FLASH™の開発においては、プロセスメカニズムの解明が重要になります。ここでは、メモリセルのデザインを決めるメモリホールエッチングについて、形状制御に関する取り組みをご紹介致します。

-

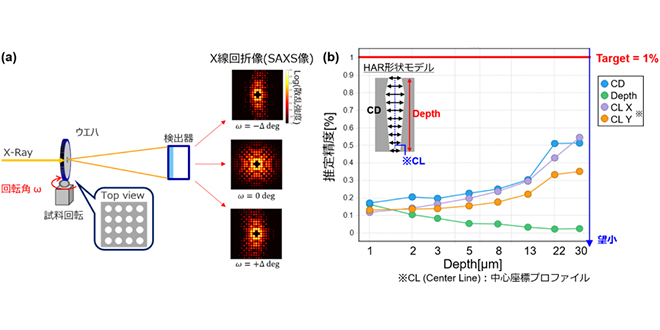

3Dメモリ製造では極小の径と極めて深い穴(高アスペクト比)の加工を行う。この制御には非破壊、高精度な測定法が必要となる。我々はT-SAXS(透過型X線小角散乱法)の測定能力をシミュレーションにより解析した。将来の3次元メモリ形状測定で必要となる0.1um径、深さ30umの構造について、精度<1%ので測定可能であることを確認した。

-

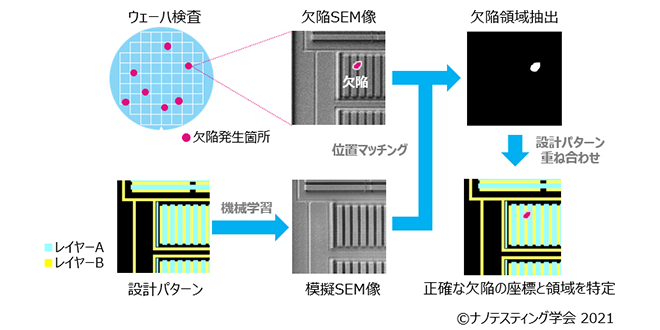

デバイス製造過程の欠陥データと設計データのデジタライゼーションにより製品完成時の電気テスト合否予測精度が大幅に向上しました。

この技術はデバイス開発のスピードアップや生産性改善に寄与しています。

-

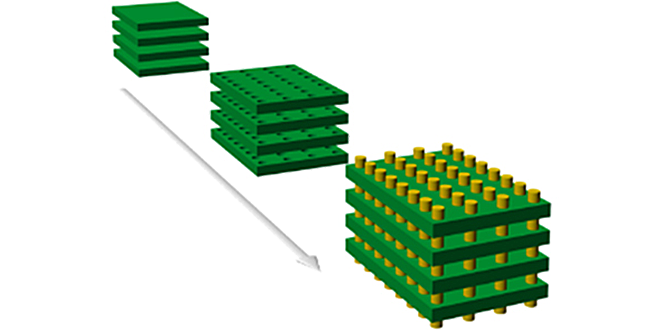

当社が開発した3次元フラッシュメモリBiCS FLASH™は、データを保存するメモリセルを作る際、板状の電極を連続で積層し、最上層から最下層まで⼀括で⽳をあけ、製造工程(プロセス)数を減らしています。この製造プロセスの中で⾮常に重要になるのが、⼀定の⽳径でより深い⽳(メモリホール)を形成するプラズマエッチング(RIE: Reactive Ion Etching)の技術です。

-

多くのデータをより小さい形で保存したい、という需要を実現するには、記憶密度を⾼めたフラッシュメモリの開発が重要です。2次元のNAND型フラッシュメモリの場合、微細化技術を中⼼に、15nmのメモリセルを開発し、その実現に寄与してきました。しかしながら技術的な限界を迎え、3次元に⾼密度(多層)化したのがBiCS FLASH™です。

キオクシアの研究部門

豊かで持続的なデジタル社会の実現のため、メモリ技術の革新により、絶え間ない技術探索とその社会実装を目指します。

当社が世界に先駆けて開発した3次元フラッシュメモリ「BiCS FLASH™」の研究開発と量産化の橋渡しを行っています。