Please select your location and preferred language where available.

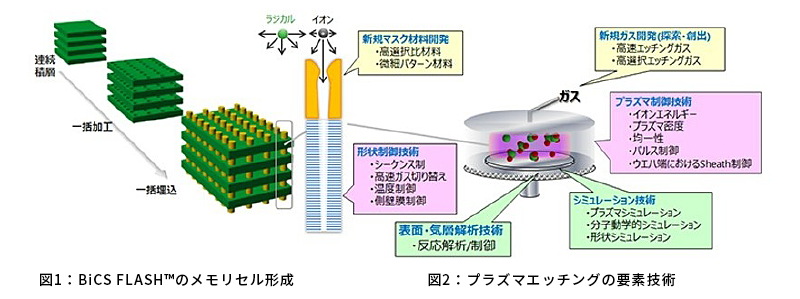

当社が開発したBiCS FLASH™は、フラッシュメモリの構造が2次元から3次元になることに伴うコストの増加を低減するために、様々な工夫をしています。例えば、データを保存するメモリセルを作る際、板状の電極を連続で積層し、最上層から最下層まで⼀括で⽳をあけ、製造工程(プロセス)数を減らしています。更に、開けられた穴に対して一括で膜を埋め込み、電極を柱状に形成することで、双⽅の電極交点を1つのメモリセルにしています(図1)。これらの製造プロセスの中で⾮常に重要になるのが、⼀定の⽳径でより深い⽳(メモリホール)を形成するプラズマエッチング(RIE*1)の技術です。最適な形状を得るためには、マスク材料やガスの新規開発のみならず、装置による形状およびプラズマ制御技術が求められます。更に、表⾯・気層の制御・および各種シミュレーション技術も駆使しながら、BiCS FLASH™の更なる⾼層化に挑戦しています。

- RIE:Reactive Ion Etching