Please select your location and preferred language where available.

CMOS directly Bonded to Array(CBA)技術とは

3次元フラッシュメモリは、現代社会を支えるinternet of things(IoT)、artificial intelligence(AI)、ビッグデータなどの各種技術の実現に不可欠な半導体デバイスです。これらの技術を実現するために、3次元フラッシュメモリの動作速度向上や消費電力低減など、性能の向上が求められています。さらに、これらの要求を低コストで実現し、安価に世界に供給できれば、より幅広い分野で、3次元フラッシュメモリを活用していただくことが可能となります。キオクシアでは、これらの要求を満たす3次元フラッシュメモリを実現するために、CMOS directly Bonded to Array(CBA)技術を開発し、量産化を実現しましたのでご紹介します。

CBA技術とは?

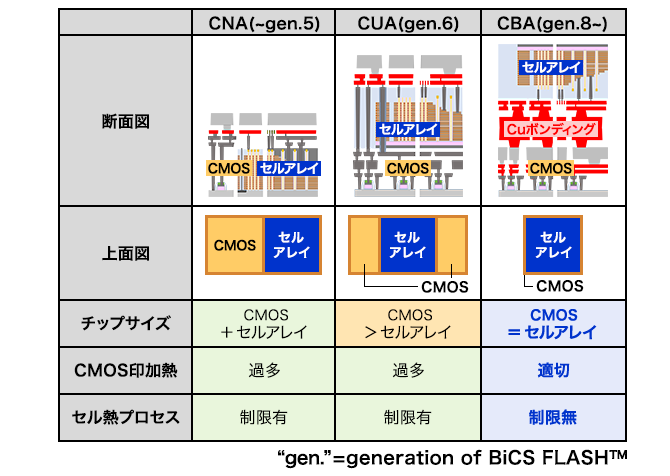

3次元フラッシュメモリは従来の2次元構造で形成されたフラッシュメモリのメモリセルを垂直方向に積み上げた構造を持っています。キオクシアで開発された3次元フラッシュメモリBiCS FLASH™の世代別構造の比較を表1に示します。

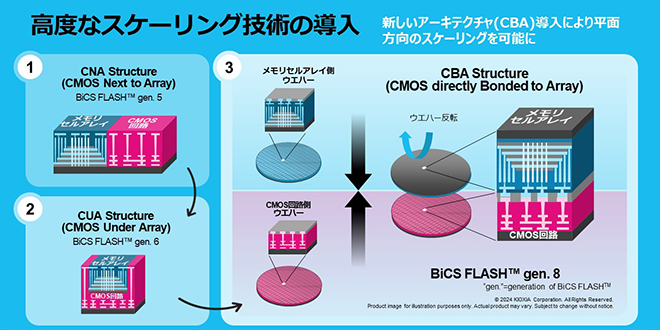

3次元フラッシュメモリの構造は大きく分けて、情報を記憶するメモリセルアレイ領域(以下セルアレイ)とセルアレイを動作させるCMOS回路領域(以下CMOS)から構成されます。BiCS FLASH™ generation 5(以下、 BiCS FLASH™ gen. と略す )までは、CMOS Next to Array(CNA)構造が採用されてきました。CNA構造では、セルアレイの横にCMOSが形成されるため、チップサイズはCMOSとセルアレイのサイズの合計とほぼ同じになります。また、CMOSを形成した後にセルアレイを形成するため、CMOSにはセルアレイ形成時の高温の熱が加わります。この高温はCMOSの特性を劣化させるため、セルアレイ形成時の熱はセル特性を維持できる最小限の温度に制限する必要がありました。

3次元フラッシュメモリのコスト削減の一つの施策は、チップサイズを小さくして300mmウエハーからより多くのチップを取得することです。そこで、BiCS FLASH™ gen. 6ではCMOSをセルアレイの下に形成するCMOS Under Array(CUA)構造が導入されました。CUA構造はCMOSを形成後、その上にセルアレイを連続的に1枚のSiウエハー上に形成するため、CNAと比較してチップサイズを縮小できます。一方で、CNAと同様にCMOSやセルアレイ形成時の温度は制限されるため、セルとCMOSの性能向上がトレードオフとなり、両立することが困難です。

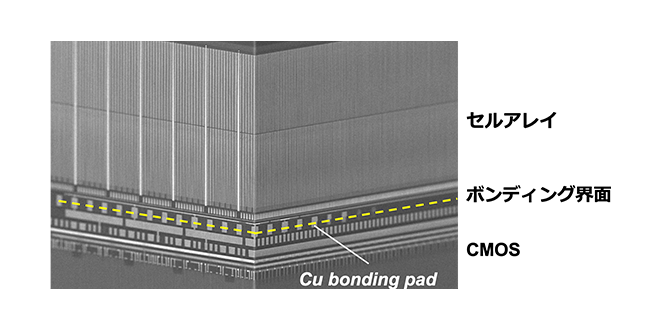

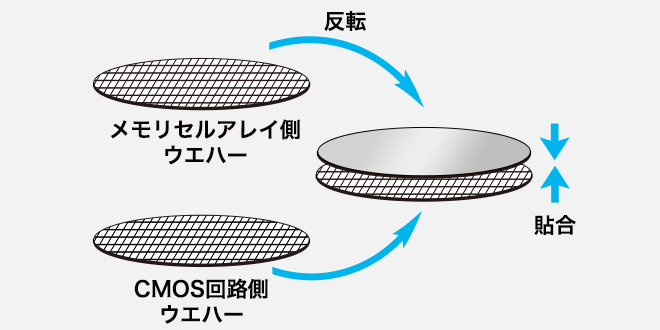

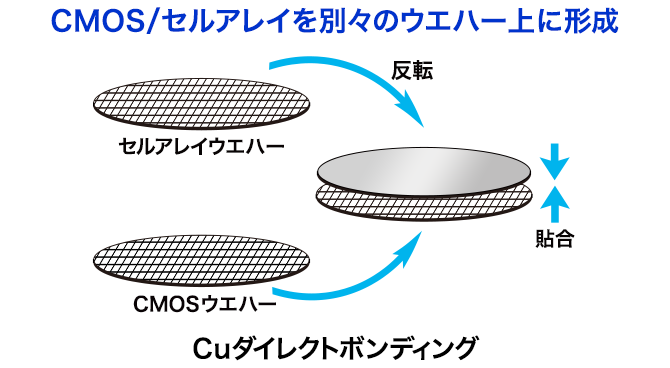

そこで提案されたのがCBA構造です。CBA構造では、CMOSとセルアレイを別々のSiウエハー上に形成した後、それぞれのウエハー上に銅(Cu)ボンディングパッドを形成します。その後、図1に示すようにSiウエハー同士をCuダイレクトボンディングプロセスで貼り合わせ、Cuボンディングパッドを介して、CMOSとセルアレイを電気的に接続することで3次元フラッシュメモリを形成します。この結果、CMOSをセルアレイと重ね合わせて形成することでチップサイズを縮小しつつ、CMOSとセルアレイはそれぞれ最適な熱プロセスを行うことが可能となり、性能向上も実現できます。

このCBA構造を実現するためにキーとなった、2つの技術を紹介します。

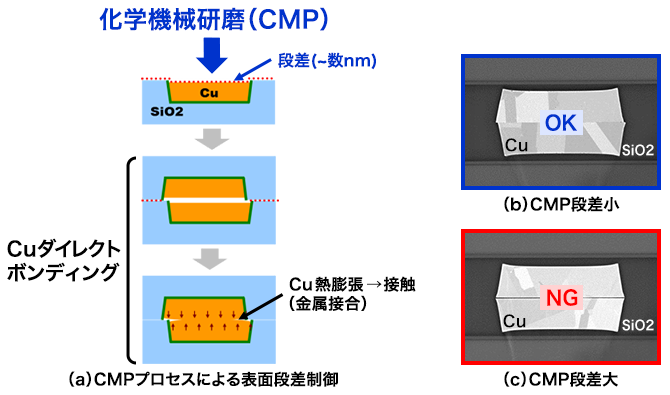

まずは、Cuボンディングパッドの段差低減技術です。前述のように、CBA構造ではCuダイレクトボンディングプロセスを用いてCuボンディングパッドとSiO2層間膜の両方を隙間なく貼り合わせる必要があります。そのため、図2(a)に示すように、CMOSおよびセルアレイウエハーの最表面に形成されたCuボンディングパッドとSiO2層間膜の段差を数 nmレベルに抑える必要があります。

この極微小な段差を制御するのが化学機械研磨(chemical mechanical polishing: CMP)プロセスです。300 mmウエハーの表面をCMPで研磨し、数 nmレベルの段差に仕上げることは、例えるなら東京ドームの中でコピー用紙1枚ほどの段差以下にするような精度のモフォロジー制御が求められます。この数nmレベルの表面段差に制御されたCMOSおよびセルアレイを有する300 mmウエハー同士を向かい合わせてSiO2層間膜表面を貼り合わせた後、アニールによりCuを熱膨張させることでCu同士が金属結合し、電気的に接続可能となります。段差が小さい場合は図2(b)のように上下のボンディングパッドのCu同士が隙間なく接続しています。一方、段差が大きいと図2(c)のように上下ボンディングパッドのCu間に隙間が生じ、電気的接続ができません。CMOSとセルアレイの間は百万個以上のCuボンディングパッドで接続する必要があるため、CBA構造では非常に高いCMPプロセス制御性を実現していることが分かります。

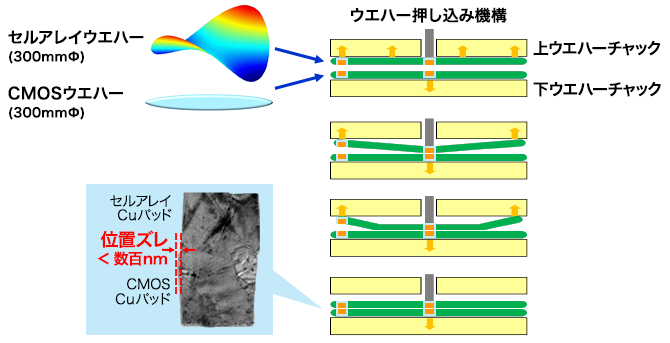

もう一つは、Cuダイレクトボンディングプロセスにおける上下ウエハー間の位置合わせ技術です。図3にCuダイレクトボンディングプロセスのシーケンスを示します。CuダイレクトボンディングプロセスではCMOSウエハーとセルアレイウエハーの表面を向かい合わせ、ウエハーの中央部から外周部に向けて徐々に近づけながら貼り合わせます。この際、300 mmウエハーの中央部から最外周部まで、CMOSとセルアレイを電気的に接続するためには、ウエハーの位置を数百 nm以下のズレに制御する必要があります。さらに、3次元フラッシュメモリのセルアレイウエハーは表1の図に示すように多数のメモリセルやワードラインが存在し、非常に大きく複雑な応力がかかっています。その結果、図3に示すように、セルアレイウエハーはポテトチップスのような複雑な反り形状になります。

この複雑な形状を持つセルアレイウエハーとほぼ反りが無いCMOSウエハーを、前述のように数百 nm以下のズレで貼り合わせています。これは例えるなら、ゴルフで200ヤード飛ばしたボールをピンからほんの数ミリもずれない位置に何度も落とすくらいの非常に微細なズレということになります。ここでもCBA構造は非常に高いCuダイレクトボンディングプロセス制御性を実現していることが分かります。

CBA構造の製品化と将来像

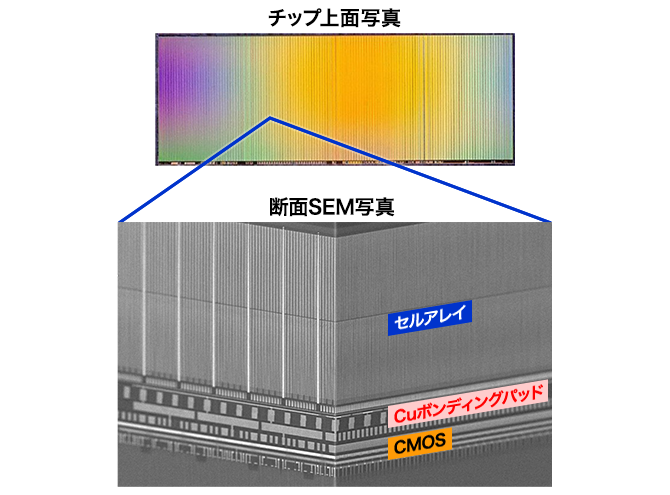

このように非常に高度なプロセス制御性を実現することにより、CBA構造はBiCS FLASH™ gen. 8で製品化されました。図4はチップの上面写真と断面SEM写真であり、CMOSとセルアレイが多数のCuボンディングパッドで接続されている様子が確認できます。このようにCMOSとセルアレイを別々に形成し、Cuボンディングパッドを介して貼り合わせることにより、セル電流は前世代比35%の向上、インターフェース速度は3.6 Gbpsの性能向上を達成しました[1][2]。

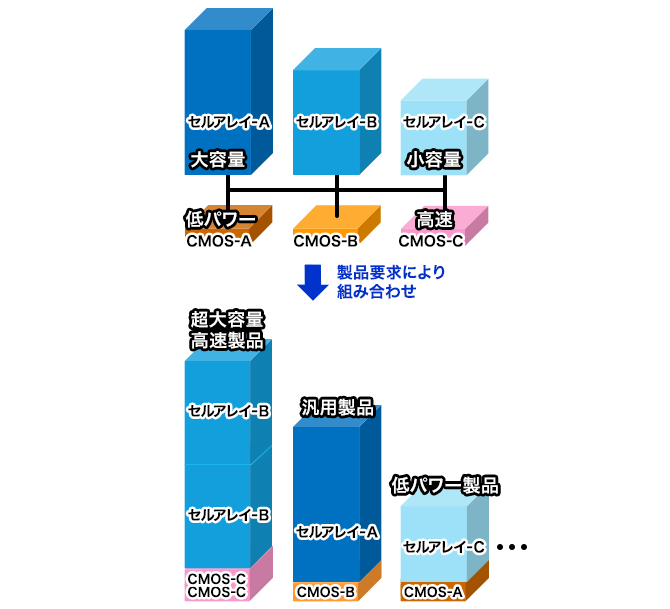

さらに、3次元フラッシュメモリの将来に向けた多様な製品要求の実現において、CBA構造は非常に有効です。図5はBiCS FLASH™ gen. 9以降の将来のCBA構造イメージを示しています。異なる性能を持つCMOSと異なる容量を持つセルアレイを組み合わせることにより、IoT、AI、ビッグデータなどの進化を支える3次元フラッシュメモリの実現が可能となります。

文献

[1] M. Tagami, "CMOS Directly Bonded to Array (CBA) Technology for Future 3D Flash Memory," in Proc. 2023 IEEE International Electron Device Meeting (IEDM).,19-5.

[2] S. Kobayashi et al., "High Performance 3D Flash Memory with 3.2Gbps Interface and 205MB/s Program Throughput based on CBA (CMOS Directly Bonded to Array) Technology," in Proc. 2023 IEEE International Electron Device Meeting (IEDM).,35-2.