Please select your location and preferred language where available.

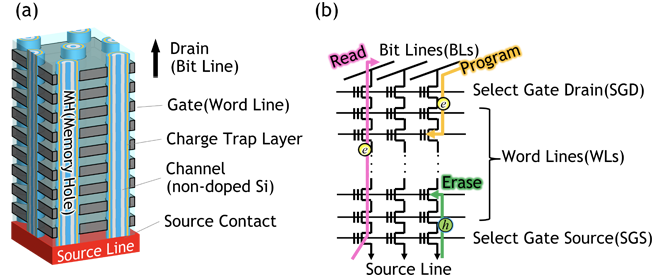

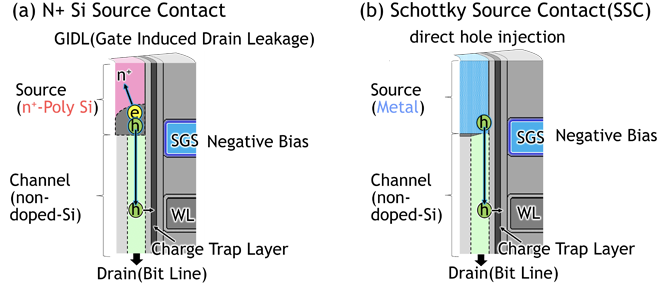

一般的な3次元フラッシュメモリは図1に示すように、メモリセルのチャージトラップ膜に対してドレインから供給される電子を注入することで書込み(Program)を行い、ソースから供給される正孔を注入することで消去(Erase)を行います。また、読込み(Read)ではソースからドレインに向けて電子が流れます。セル密度を高めるためにはメモリセルのWL(Word Line)積層数を増やしていく必要がありますが、WL積層数の増加に伴いセル動作のためにより多くの電子および正孔を供給することが求められます。

Copyright (2025) The Japan Society of Applied Physics[2]

しかし、従来のN+ -Siソース接合構造では、ソース接合部に存在しない正孔をゲート誘導ドレインリーク(Gate Induced Drain Leakage:GIDL)により生成しなければならず、将来的にWL積層数が増加すると、それに対応した量の正孔を供給することができず、消去速度が低下することが懸念されていました。そこで、私たちはショットキーソース接合構造という新たな構造を考案・開発し、動作実証を行いました。

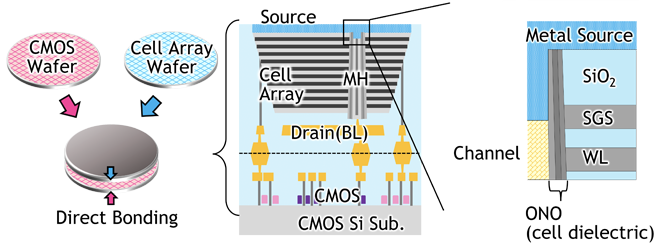

私たちは、CMOS回路とメモリセルを別々のウエハ上に形成し、貼合により配線するCBA(CMOS directly Bonded to Array)構造の3次元フラッシュメモリを世界に先駆けて開発し、業界内で高い競争力を持っています[1]。ショットキーソース接合構造は、貼合プロセスにより表裏反転したCBA構造のメモリセル表面(ソース側)からチャネル上に金属材料を成膜し、真性半導体であるチャネルとのショットキー接合を形成します(図2)。

Copyright (2025) The Japan Society of Applied Physics[2]

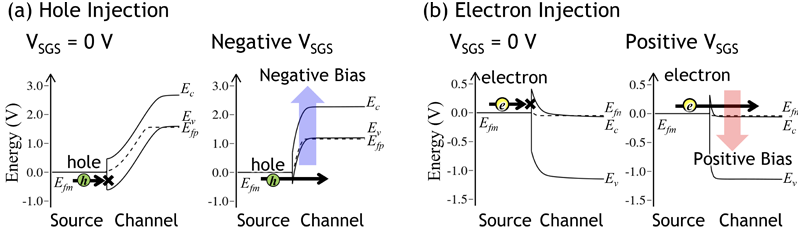

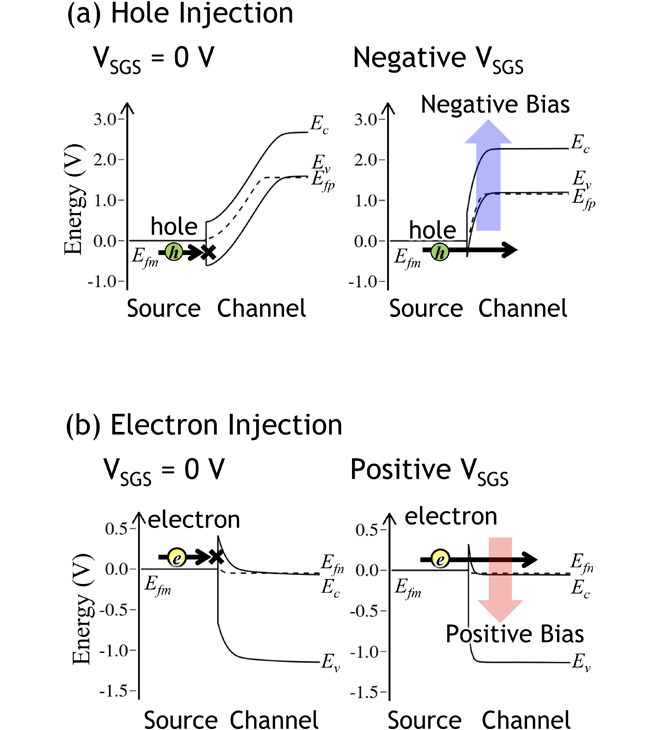

図3のバンド図に示すように、ショットキー接合はそのままでは電子と正孔の供給を妨げる方向に整流特性を持ちますが、この接合構造に絶縁膜を隔てて近接した選択ゲート(Select Gate Source:SGS)から正負の電界をかけることにより、それぞれ電子と正孔のオーミック接合が得られます。

Copyright (2025) The Japan Society of Applied Physics[2]

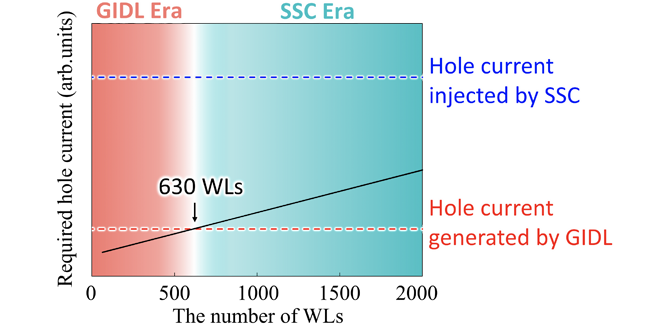

ショットキーソース接合構造は、この電子と正孔の両方をソースから供給することができるというアンバイポーラ的特性を持っています。この特性により、従来の基本的なセルアレイ動作を踏襲しつつも、ゲート誘導ドレインリークにより正孔を供給する従来のN+ -Siソース接合構造と比べて劇的に消去速度を改善することが期待されます(図4)。

Copyright (2025) The Japan Society of Applied Physics[2]

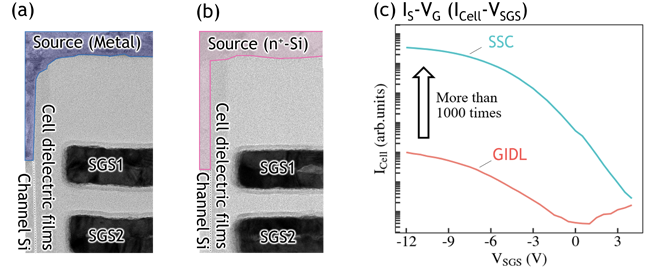

ショットキーソース接合構造の基本動作検証のため、本構造を有するセルTEG(Test Element Group)を試作しました(図3(a))。消去電流を評価した結果、ショットキーソース接合構造はN+ -Siソース接合構造と比べて1000倍以上もの消去電流が得られることが分かりました(図3(c))。

Copyright (2025) The Japan Society of Applied Physics[2]

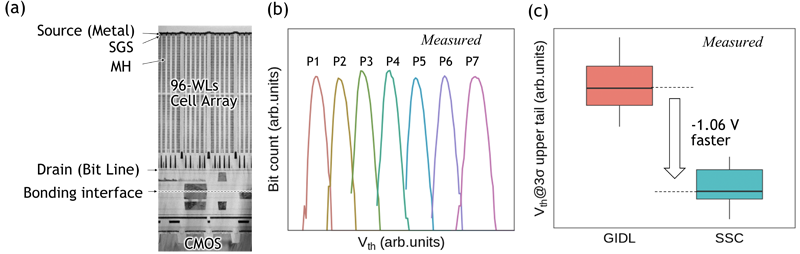

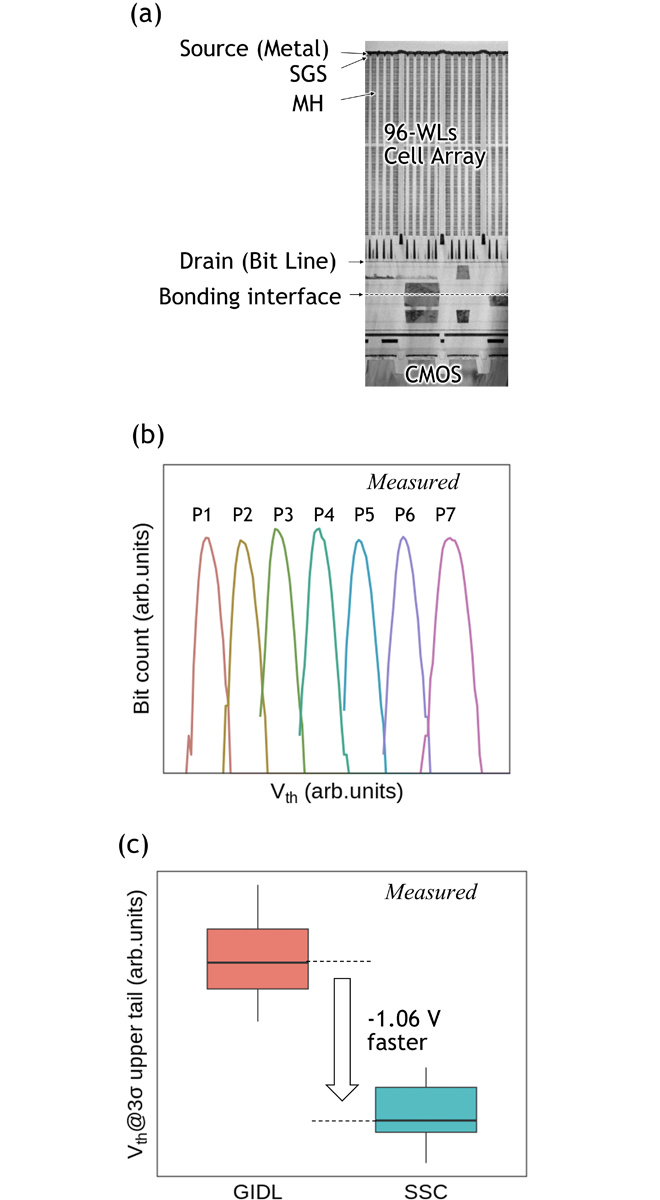

セルアレイ動作を検証するため、ショットキーソース接合構造を搭載したCBA構造のWL96層3次元フラッシュメモリを開発し、3ビット/セル書込み(Triple level cell TLC)のセルアレイ動作に成功しました。また、消去動作中の閾値電圧分布からショットキーソース接合構造の適用により消去速度が改善することを確認しました。

Copyright (2025) The Japan Society of Applied Physics[2]

セルアレイ動作検証の結果から、将来のWL積層数に対する消去トレンドを見積もりました(図7)。従来のN+ -Siソース接合構造ではWL630層から消去速度が劣化し始めますが、ショットキーソース接合構造ではWL1000層以上でも十分な消去電流を供給できます。ショットキーソース接合構造は将来の超高積層3次元フラッシュメモリにおける消去動作を実現するブレイクスルー技術となることが期待されます。

Copyright (2025) The Japan Society of Applied Physics[2]

本研究成果は、Sandisk Corporationとの共同開発に基づき、2025年6月に開催された国際会議2025 Symposium on VLSI Technology and Circuitsにおいて発表されました[2]。

文献

[1] Masayoshi Tagami, “CMOS Directly Bonded to Array (CBA) Technology for Future 3D Flash Memory”, 2023 IEEE International Electron Devices Meeting (IEDM).

[2] Susumu Hashimoto et al., “A Schottky junction as a hole injector for enhancing erase operation of 3D flash memory in CMOS Directly Bonded to Array (CBA) era with over 1,000 word lines”, 2025 IEEE Symposium on VLSI Technology and Circuits, T9-1.