Please select your location and preferred language where available.

二端子メモリ素子を使った高速で大容量な次世代メモリの開発が世界的に進められていますが、現在はその容量が最大でも数百ギガビットに留まっています。我々はさらに将来を見据えて、テラビットを超える超大容量のクロスポイント型メモリを実現するための課題を抽出し、それを解決するための新規メモリ開発を進めています。

テラビット級の超大容量二端子メモリを実現するためには、メモリ素子の動作電流低減という新たな課題を克服しなければなりません。最近の研究によれば、メモリ素子の動作電流をマイクロアンペア以下に抑えなければ配線の電圧降下や消費電力の問題を解決できないことが示されています[1]。

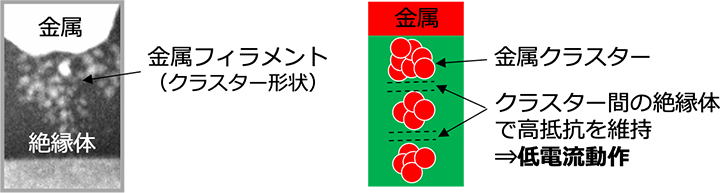

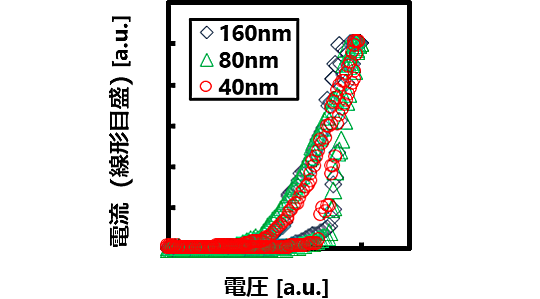

我々は、マイクロアンペア以下の低電流動作が期待される新たな二端子メモリ「銀イオンメモリ」に注目し、開発を進めています。イオンメモリは、金属と絶縁体から構成されるシンプルな構造で、絶縁体中に形成される金属フィラメントを電圧制御することでON(低抵抗)状態とOFF(高抵抗)状態を実現します。最適な金属と絶縁体の組み合わせを選択すれば、クラスター形状の金属フィラメントとなり(図1)、他のメモリ素子に比べて低電流(高抵抗)なON状態を形成できます。

本技術については、2019年6月に京都で開催された国際学会「VLSIシンポジウム」において発表を行いました(2)。

[1] Z. Jiang, S. Qin, S. Fujii, D. Lee, S. Wong, and H.-S. P. Wong , “Selector requirements for Tera-bit Ultra-High-Density 3D Vertical RRAM”, 2018 IEEE Symposium on VLSI Technology, pp.107-108.

[2] S. Fujii, R. Ichihara, T. Konno, M. Yamaguchi, H. Seki, H. Tanaka, D. Zhao, Y. Yoshimura, M. Saitoh, and M. Koyama, “Ag Ionic Memory Cell Technology for Terabit-Scale High-Density Application”, 2019 IEEE Symposium on VLSI Technology, pp.T188-T189.