Please select your location and preferred language where available.

世界中で日々生成されるデジタルデータは急速に増加しており、2025年には、世界のデータスフィアと呼ばれるデータの総量が175 ZBに達すると言われています。現在のところ、これらの大量なデータはデータセンターやサーバー等にある大容量ストレージに保存されており、そこではHDDやSSDが使われています。さらに、SSDは、データの読み書きの速度、消費される電力、装置のサイズ等の面でHDDよりも優れているため、SSDによるHDDの置き換えが進んでいます。これを実現しているのが、フラッシュメモリの継続的なビットコストのスケーリングです。フラッシュメモリのビットコストスケーリングは、3次元方向へのメモリセルの高積層化と一つのメモリセルに多くのビット情報を入れる多値化によって進められています。

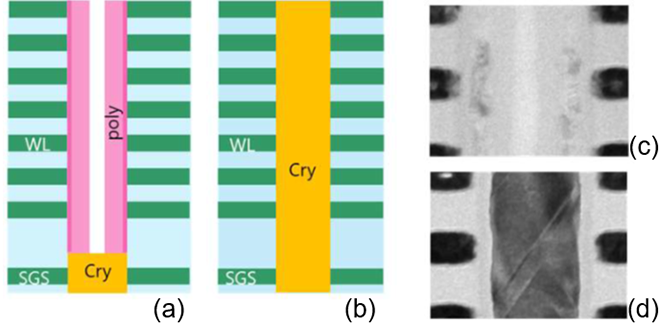

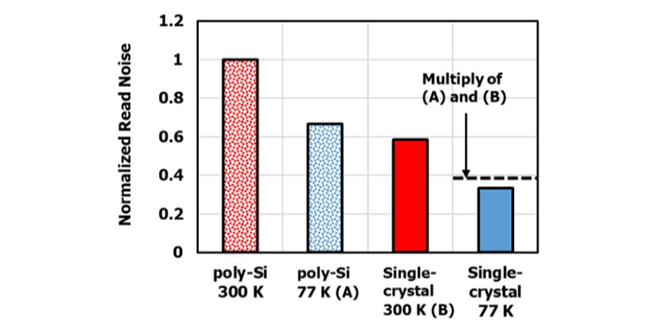

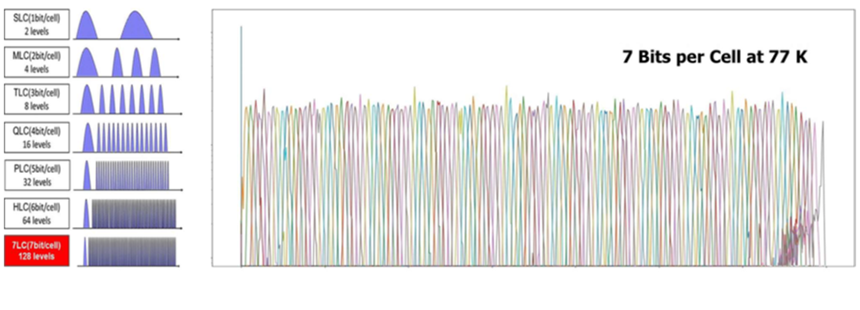

以前、我々は、3次元フラッシュメモリ(BiCS FLASHTM)の極低温動作によるストレージ性能の向上と6ビットセルの実証を報告しました。[1, 2]今回は、そこからさらに一歩進んで、メモリセルの特性を向上させるシリコンプロセス技術と極低温動作とを組み合わせることにより、世界で初めて7ビット/セルの実証に成功しました。具体的には、メモリセルを構成しているセルトランジスタのチャネル部の材料を、従来の多結晶シリコンから、単結晶シリコンに変えました。(図1)フラッシュメモリの読み出し動作では、メモリセルのしきい値電圧(Vth)を判別してビット情報に変換していますが、Vthには読み出しノイズと呼ばれる変動があります。この読み出しノイズは、極低温動作と単結晶シリコンを使うことにより大幅に小さくすることができます。(図2)その結果、より大きな多値化を実現しやすくなり、7ビット/セルでは1つのメモリセルに128(27)レベルのVth分布を作り出しています。(図3)現在量産されているフラッシュメモリで最も多値化が大きいものは4ビット/セルですが、我々の提案する7ビット/セルでは、極低温への冷却コストも含めてビットコストを大幅に下げることが可能となる見込みです。

将来において、シリコンテクノロジーによる最小のビットコストと、そのビットコストの継続的なスケーリングを実現するために、我々キオクシアの研究所は、今後も極低温に冷却して動作させる低温メモリ技術の開発に取り組んでいきます。

本研究は、2022年5月に開催された国際会議IMW (International Memory Workshop)に採択され発表されています。[3]

本稿は、文献[3]@2022 IEEEから図面等一部抜粋&再構成したものです。

文献

[1] Y. Aiba, H. Tanaka, T. Maeda, K. Sawa, F. Kikushima, M. Miura, T. Fujisawa, M. Matsuo, and T. Sanuki, ” Cryogenic Operation of 3D Flash Memory for New Applications and Bit Cost Scaling with 6-Bit per Cell (HLC) and beyond”, 2021 5th IEEE Electron Devices Technology and Manufacturing Conference, EDTM 2021, 9421051

[2] T. Sanuki, Y. Aiba, H. Tanaka, T. Maeda, K. Sawa, F. Kikushima, and M. Miura, “Cryogenic Operation of 3-D Flash Memory for Storage Performance Improvement and Bit Cost Scaling,” in IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, 2021, vol. 7, no. 2, pp. 159-167

[3] H. Tanaka, Y. Aiba, T. Maeda, K. Ota, Y. Higashi, K. Sawa, F. Kikushima, M. Miura, and T. Sanuki, “Toward 7 Bits per Cell: Synergistic Improvement of 3D Flash Memory by Combination of Single-crystal Channel and Cryogenic Operation,” 2022 IEEE International Memory Workshop (IMW), 2022, pp. 1-4