Please select your location and preferred language where available.

BiCS FLASH™はワード線の積層数を増やすことによって記録密度を向上させ、コストを下げることができます。しかし、高積層化は積層構造中を縦に貫く電流チャネルの直流抵抗を増加させ、読出し電流を減少させるため、読出し速度が低下します。高積層化してもメモリの読出し速度を維持するための一つの方法として、サイリスタ構造が提案されています(例えば[1]、[2]))。この度我々は3Dストリングの実測とTCADシミュレーションを駆使してサイリスタ構造を解析しました。

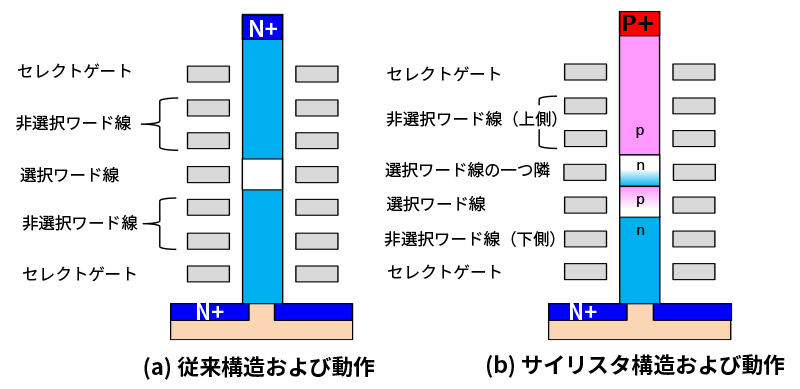

従来のセルでは、半導体中に負電荷を供給するN型不純物を導入した領域(N+)が電流チャネルの両側にあります(図1(a))。選択ワード線に正の読出し電圧を印加したとき、負電荷が誘起されればチャネルがつながってオンとなり、誘起されなければチャネルがつながらずオフとなります。

これに対して、サイリスタ構造では、電流チャネルの下端にはN+領域が、上端には正電荷を供給するP型不純物を導入した領域(P+)が構成されます(図1(b))。下側の非選択ワード線には正の読出し転送電圧を、上側の非選択ワード線に負の読出し転送電圧を印加して使用します。オフ状態では選択ワード線に負電圧を印加して負電荷に対する障壁を作り、ひとつ隣のワード線に正電圧を印加して正電荷に対する障壁を作ります。すると、チャネル中の電荷は仮想的な正負正負(PNPN)の領域を構成します。これは、電力用半導体デバイス等で使われているスイッチング素子であるサイリスタと同様のPNPN構造になっています。選択ワード線の電圧を上げて閾値を超えたとき、サイリスタの障壁は一気に崩れるため、大電流が流れるようになります。

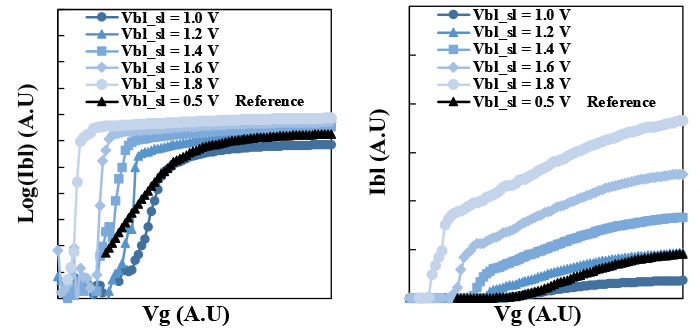

図2に従来動作とサイリスタ動作のメモリセル電流(Ibl)の電流電圧特性を示します。従来動作(黒太線)と比較して、サイリスタ動作ではオフからオンへの急峻な電流の立ち上がりが見られます。また、オン状態の電流値が従来動作よりも大きいことがわかります。

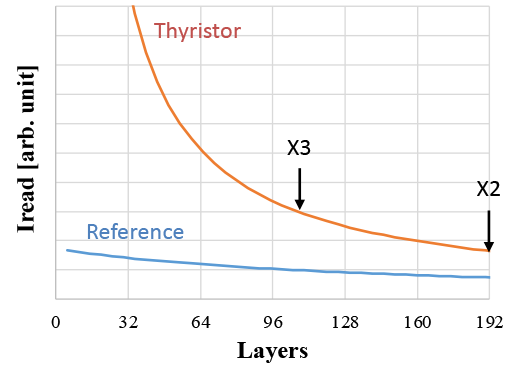

TCADシミュレーションによる我々の試算によると、サイリスタ動作では、適切な端子電圧を設定すれば、200層近く積層したとしても、従来の2倍の読出し電流を確保できることが分かりました(図3)。

しかし、サイリスタ動作には、重大な解決すべき課題がありました。あるメモリセルへの書込みによって、それに隣接するメモリセルの閾値電圧が変動するという強力なセル間干渉効果です。この原因は、前に述べた正電荷に対する障壁が隣のメモリセルに書込まれた電子の負電荷によって減少するためです。したがって、セル間干渉効果を抑制するためには、隣のメモリセルへの書込みが影響しない程度まで、正電荷に対する障壁を補強しておけばよいことになります。しかし、ワード線の正電圧を上げることで障壁を高くしようとしても、プログラムディスターブが発生するため印加できる電圧には限度があります。我々は、選択ワード線に隣接する非選択ワード線を2本使うことによって、元のサイリスタ動作と同じ電圧のままで、正電荷に対する障壁を補強できることを示しました。この改良型の読出し動作を導入することによって、1セルに4ビットの情報を記録するQLCにおいて、読出し速度を20 %、書込み速度も15 %向上させることができます。

本研究成果は2020年5月に開催された国際会議IMW2020において報告いたしました[3]。

[1] S.-M. Joe, H.-J. Kang, N. Choi, M. Kang, and B.-G. Park, IEEE Trans. Elec. Dev. Vol.63, No.4, 1533 (2016).

[2] N. C. Choi, H.-J. Kang, S.-H. Bae, B.-G. Park and J.-H. Lee, 2017 Symposium on VLSI Technology Digest of Technical Papers, T15-2 (2017).

[3] H. Horii, T. Maeda, and T. Sanuki, ” Thyristor Operation for High Speed Read/Program Performance in 3D Flash Memory with Highly Stacked WL-Layers” 2020 IEEE International Memory Workshop, IMW 2020 – Proceedings 9108147

本稿は、文献[3]@2020 IEEEから図面等一部抜粋&再構成したものです。

記載されている社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。