Please select your location and preferred language where available.

低消費電力で集積度の高いAI(人工知能)向けインメモリコンピューティングの実現に向け、強誘電膜としてHfO2を用いた強誘電メモリが近年注目を集めています。代表的な強誘電メモリとしては、MIS*1トランジスタのゲート絶縁膜に強誘電膜を適用したFeFET(Ferroelectric FET)と、2つの電極で強誘電膜を挟み込んだFTJ(Ferroelectric Tunnel Junction)が挙げられますが、FeFETはCMOS-LSIとの整合性が非常に高いため、特に有望視されています。

このFeFETの課題の一つは、メモリウィンドウ(強誘電膜の分極反転によって生じる閾値電圧の変化量)が小さいことです。これまでにもFeFETのメモリウィンドウの制限要因に関する研究は行われてきましたが[1]、定量的な要因解明には至っていませんでした。

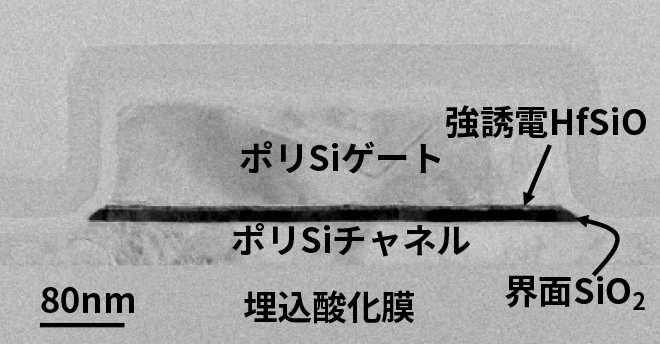

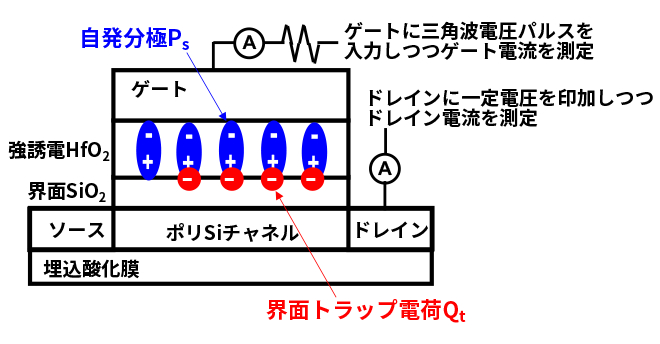

今回私達は、強誘電膜としてHfSiOを用いたポリSiチャネルFeFETを作製し(図1)、このFeFETに対して、メモリ動作中のゲート電流とドレイン電流を両方測定することにより、強誘電膜中に生じる自発分極量Psと、強誘電膜とその下のシリコン酸化膜の間の界面に生じるトラップ電荷量Qtを抽出する新解析手法(図2)を適用しました。

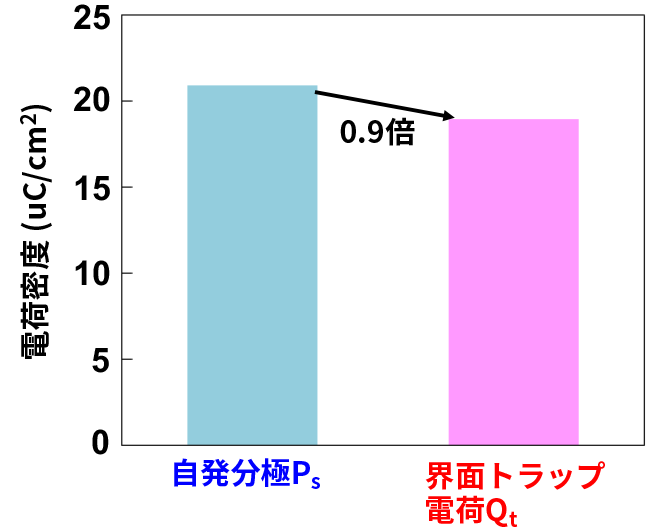

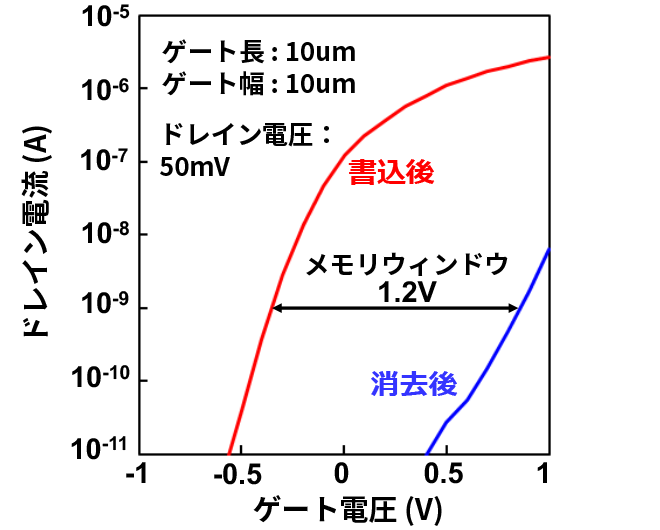

この結果、自発分極量の約9割にも及ぶトラップ電荷量が界面に発生しており(図3)、自発分極の大半がトラップ電荷によって相殺されるためにメモリウィンドウが1V程度に制限されることを明らかにしました(図4)。

この成果は、AI応用向け高性能FeFETの実現に向けた大きな一歩であると考えられます。

本技術は2020年12月に開催された国際学会IEDM (International Electron Devices Meeting) において招待講演を行いました[2]。

本稿は、文献[2]@2020 IEEEから図面等一部抜粋&再構成したものです。

記載されている社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。

- MIS: Metal Insulator Semiconductor

[1] K. Ni, P. Sharma, J. Zhang, M. Jerry, J. A. Smith, K. Tapily, R. Clark, S. Mahapatra, and S. Datta, “Critical Role of Interlayer in Hf0.5Zr0.5O2 Ferroelectric FET Nonvolatile Memory Performance,” IEEE Trans. Electron Devices, vol.65, no.6, pp.2461-2469 (2018).

[2] M. Saitoh, R. Ichihara, M. Yamaguchi, K. Suzuki, K. Takano, K. Akari, K. Takahashi, Y. Kamiya, K. Matsuo, Y. Kamimuta, K. Sakuma, K. Ota, and S. Fujii, “HfO2-based FeFET and FTJ for Ferroelectric-Memory Centric 3D LSI towards Low-Power and High-Density Storage and AI Applications”, 2020 IEEE IEDM, pp.375-378.