Please select your location and preferred language where available.

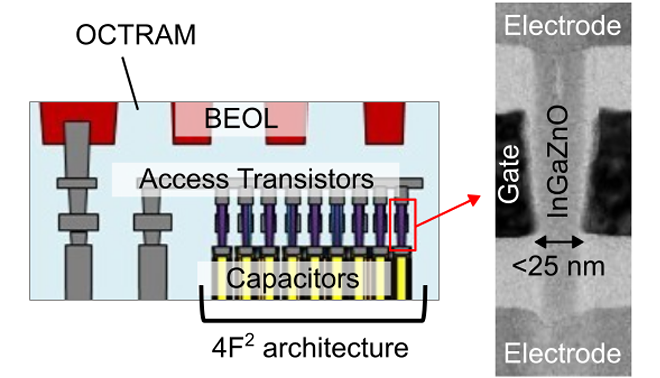

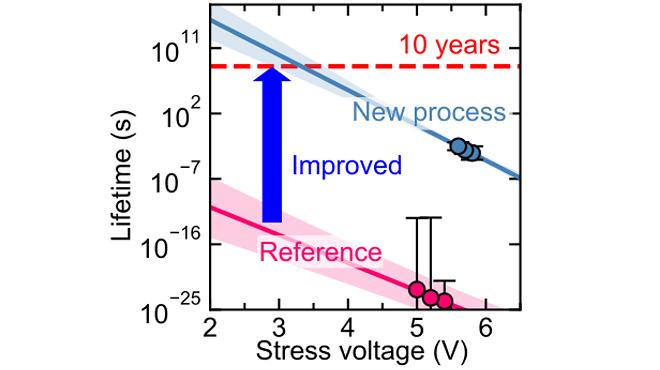

Improvement of Time-Dependent Dielectric Breakdown in Sub-25 nm Gate-All-Around Vertical InGaZnO Transistor for 4F2 DRAM Application

September 18, 2025

Rapid evolution of computers and artificial intelligence (AI) requires low power and high-performance memories. Oxide-Semiconductor Channel Transistor DRAM (OCTRAM), a new type of DRAM technology, can offer significant advantages in power saving compared to conventional DRAM [1]. To realize the new DRAM, we conducted a thorough assessment of reliability in oxide-semiconductor channel transistor with a scaled dimension below 25nm (Figure 1). In this study, we focused on the time-dependent dielectric breakdown (TDDB) lifetime. We found that the lifetime degradation was caused by two separated factors, namely an intrinsic factor due to dimensional scaling and an extrinsic factor by fabrication process. Process optimization to minimize the extrinsic degradation achieved a highly reliable transistor with an estimated TDDB lifetime over 10 years (Figure 2). This result demonstrates that the scaled oxide-semiconductor channel transistor is promising for future low-power and high-density memory with high reliability.

Copyright (2025) The Japan Society of Applied Physics

Copyright (2025) The Japan Society of Applied Physics

This achievement was presented at 2025 IEEE Symposium on VLSI Technology and Circuits.

Reference

[1]KIOXIA Corporation. Kioxia Develops OCTRAM (Oxide-Semiconductor Channel Transistor DRAM) Technology. Accessed August 25, 2025.

[2] A. Kamiyama et. al., “First Thorough Assessment of Time-Dependent Dielectric Breakdown in Sub-25 nm Gate-All-Around Vertical InGaZnO Transistor for 4F2 DRAM Application”, 2025 IEEE Symposium on VLSI Technology and Circuits, T20-3.