Please select your location and preferred language where available.

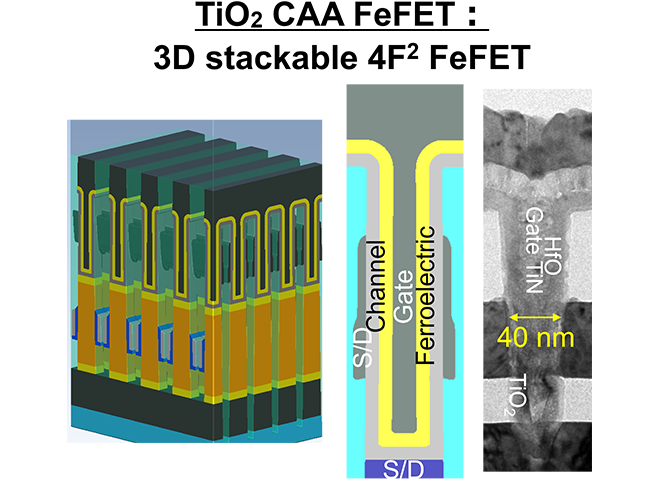

私たちは、次世代の高速大容量メモリの候補として、縦型チャネルオールアラウンド型のTiO2チャネル強誘電体トランジスタ(TiO2 CAA FeFET)の開発を進めています 図1 [1]。高速メモリには高い駆動電流が必要です。本研究では、TiO2 CAA FeFETの駆動電流改善に向けて、寄生抵抗発現メカニズムを詳細に調査し、改善指針を構築しました。

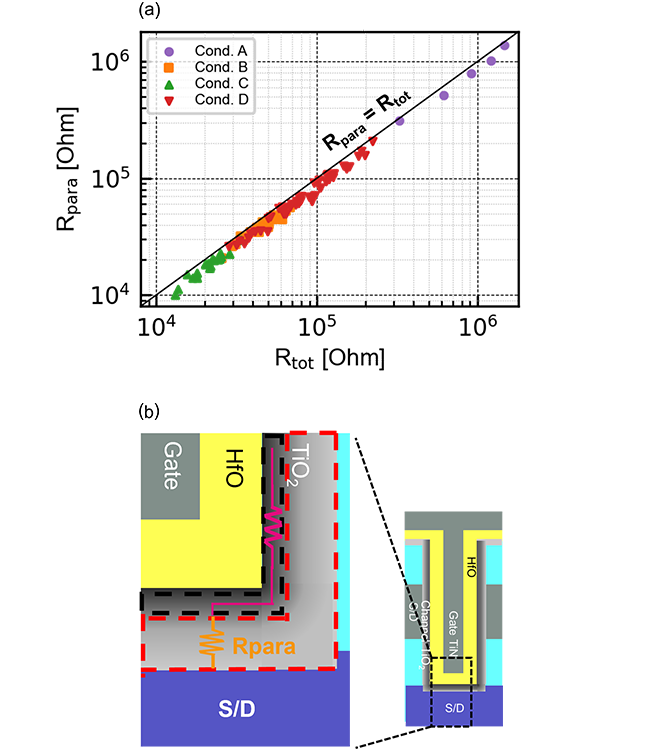

図2(a)には、詳細な電気特性評価により抽出したTiO2 CAA FeFETの寄生抵抗成分(Rpara)と素子の総抵抗(Rtot)の関係を示します。総抵抗のおよそ85%が寄生抵抗成分であり、比率は素子構造や形成プロセスに依存せずほぼ一定であることが分かりました。このことから、TiO2 CAA FeFETの寄生抵抗成分は一般的なトランジスタの寄生抵抗とは異なり、蓄積していないチャネル領域が主成分であることを提案しました 図2(b)。

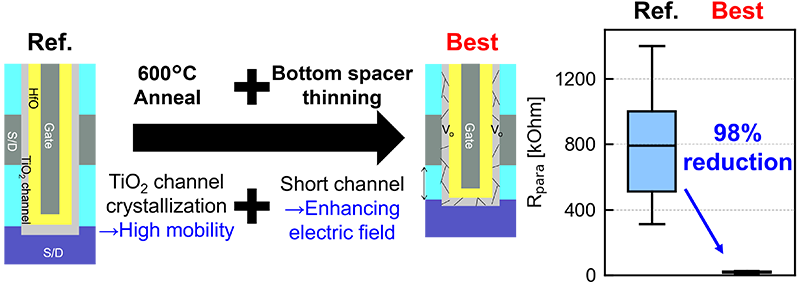

チャネル領域が寄生抵抗成分であることから、チャネル形成プロセスの改善やチャネルに印加される電界の増大が抵抗低減に大きく寄与します。追加アニールによるTiO2チャネルの結晶化やソースドレイン電極の材料最適化によりTiO2チャネルの移動度やキャリア密度を改善し、さらに、ソースドレイン間のスペーサー膜厚を薄膜化し電界を強めることで、寄生抵抗を従来よりも98%低減することに成功しました 図3。

本研究により、TiO2 CAA FeFETの寄生抵抗発現メカニズムと改善指針が明らかになり、98%の寄生抵抗を低減することに成功しました。今回実証した改善指針を元に、今後高速メモリ実現に向けてさらなる特性改善が期待されます。

©2025 JSAP

©2025 JSAP

©2025 JSAP

本成果は2025年9月に開催された2025 International Conference on Solid State Devices and Materialsにおいて発表されました。

文献

[1] S. Kabuyanagi et. al., “A Vertical Channel-All-Around FeFET with Thermally Stable Oxide Semiconductor Achieving High ΔIon > 2μA/cell for 3D Stackable 4F2 High Speed Memory”, 2024 IEEE Symposium on VLSI Technology and Circuits, T8-2.

[2] K. Kawaguchi et. al., “Mechanism and Mitigation of Parasitic Resistance in Vertical TiO2 Channel-All-Around FeFET towards High-Speed Memory Application”, 2025 International Conference on Solid State Devices and Materials.