Please select your location and preferred language where available.

One-Pulse-Programmable Multi-Level PCM/Selector Cross-Point Memory

November 29, 2023

Cross-point memory composed of Phase change memory(PCM) and Selector has been widely developed as a large-capacity and high-speed nonvolatile memory. In order to realize larger memory capacity in the future, multi-level memory cell is desired. However, the conventional multi-level technology uses multiple pulses, which results in degradation of programming speed. To solve this problem, we have proposed and demonstrated a multi-level programming technique using just one single pulse by optimizing the PCM composition and the electrode structure.

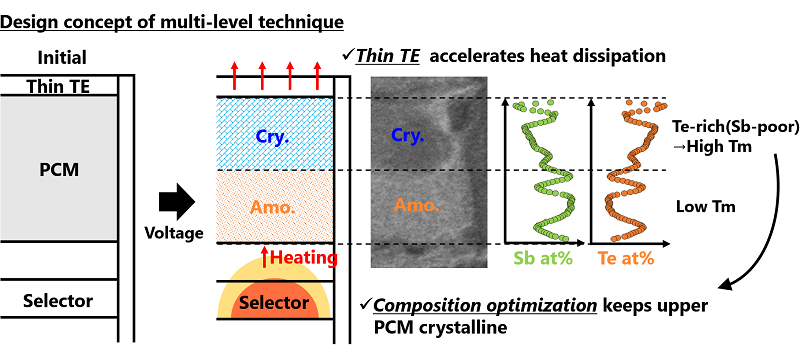

The concept of the multi-level programming technique is shown in Figure 1. The phase change of PCM proceeds by the heat generated from the Selector. We used a thinner top electrode to accelerate heat dissipation and suppress temperature rise in the upper layer of PCM. Moreover, the upper layer of PCM was designed with a Te-rich composition to be a higher melting point. As a result, we succeeded in shifting the timing of the phase change between the upper and lower layers of PCM.

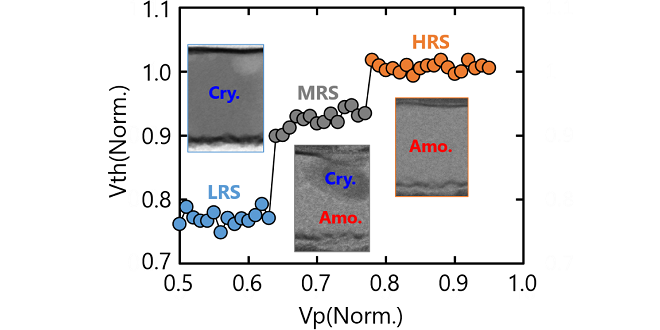

Figure 2 shows the relationship between Selector threshold(Vth) and programming voltage(Vp). We have succeeded in forming the distinct middle resistance state(MRS) between the low resistance state(LRS) and high resistance state(HRS), where crystalline and amorphous co-exist.

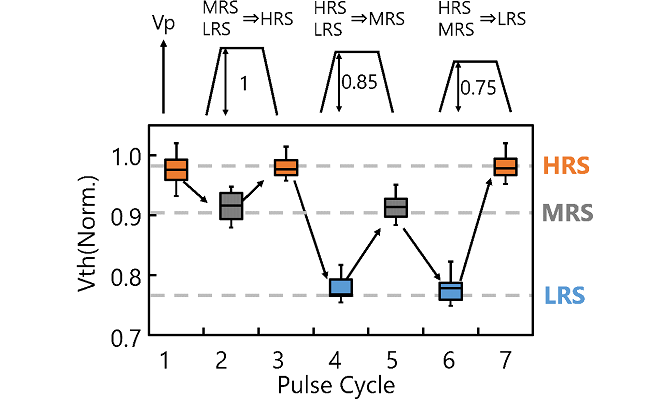

We also demonstrated that programming to these three states can be achieved with a single pulse and, therefore, there is no degradation in programming speed compared to conventional technology(Figure 3).

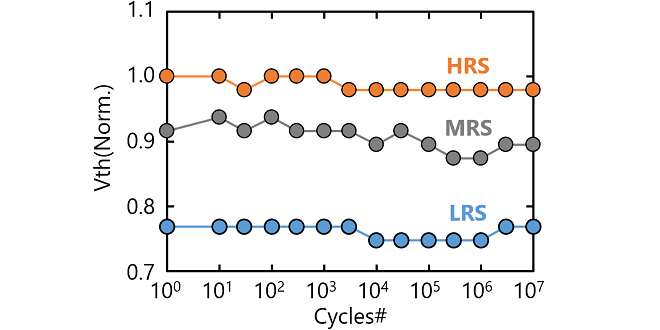

Cycling endurance evaluation(Figure 4) shows that the three states can be maintained after 107 programming operation with unchanged Vth value. These results indicate that our one-pulse-programmable multi-level technique is a promising technology which can increase memory capacity without degradation in programming speed.

This was presented at ESSDERC 2023(European Solid State Device Research Conference 2023).

Reference

[1] Y. Matsuzawa et al., "One-Pulse-Programmable Multi-Level PCM/Selector Cross-Point Memory for 20 nm Half Pitch and Beyond," ESSDERC 2023 - IEEE 53rd European Solid-State Device Research Conference (ESSDERC), Lisbon, Portugal, 2023, pp. 25-28, doi: 10.1109/ESSDERC59256.2023.10268477.