Please select your location and preferred language where available.

Recovery of cycling-induced degradation of interfacial SiO2 in HfO2-FeFET and its impact on retention characteristics

November 15, 2023

FeFET (Ferroelectric FET) is a non-volatile memory based on Vth (threshold voltage) modulation, caused by spontaneous polarization (Ps) reversal in the ferroelectric layer. HfO2 based FeFET has gained much attention as emerging memory, due to its CMOS compatibility, high-speed and low-voltage operation.

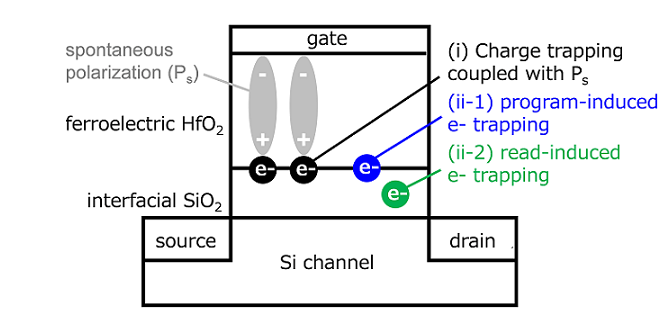

In FeFET with interfacial layer SiO2, besides Ps reversal, various kind of charge trapping occurs such as (i) charge trapping coupled with Ps, (ii-1) program induced e- trapping and (ii-2) read induced e- trapping (Figure 1)[1]. In this study, we investigate the impact of (ii-2) read induced e- trapping on the retention characteristics of FeFET.

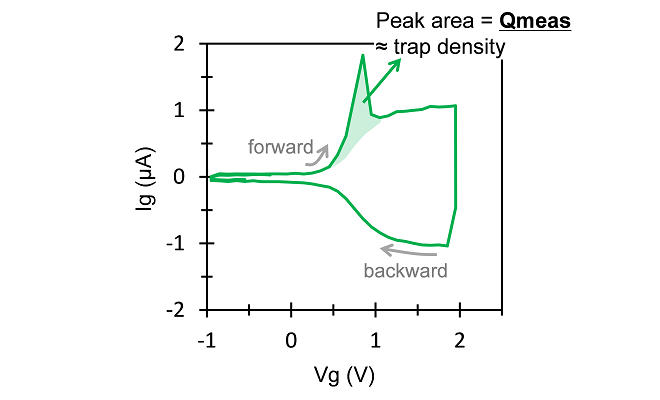

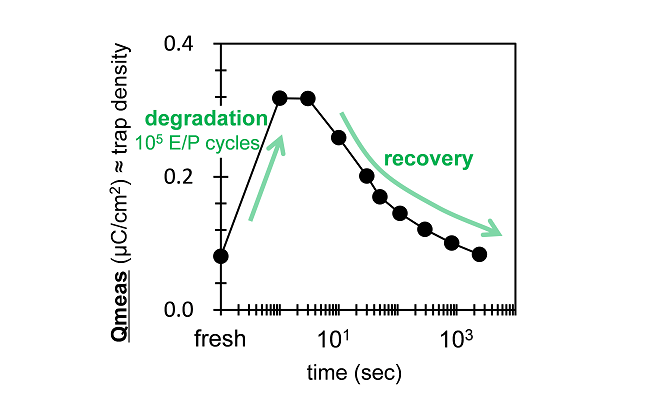

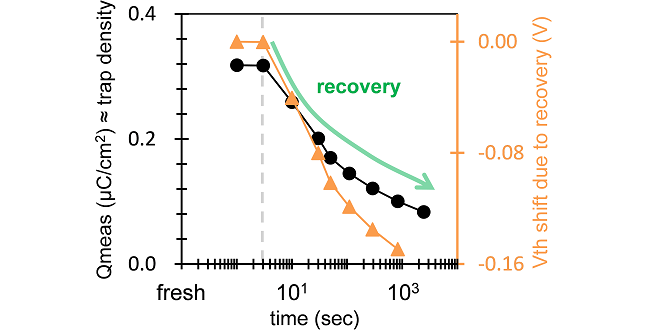

By monitoring the transient gate current during read operation (Figure 2(a)), the time evolution of (ii-2) trap sites related to read induced e-trapping was quantitatively extracted. Figure 2(b) shows, that erase/program cycling generated new trap sites, capturing electrons during read operation, disappear within one hour at room temperature.

during read operation

105 Erase (E)/Program (P) cycling

and during retention process[2]

The recovery of these trap sites causes a non-negligible negative Vth shift during long time retention process (Figure 3). We found, that the understanding of both cycling degradation and the following recovery is necessary to improve the retention characteristics in FeFET.

Copyright (2023) The Japan Society of Applied Physics

These results were presented at the international conference SSDM 2023.

Reference

[1] R. Ichihara et al., IEDM, 131 (2021).

[2] V. Schlykow et al. SSDM Ext. Abstr. p.435 (2023).