Please select your location and preferred language where available.

Novel Operation Scheme for Suppressing Disturb in HfO2-based FeFET Considering Charge-Trapping-Coupled Polarization Dynamics

June 7, 2023

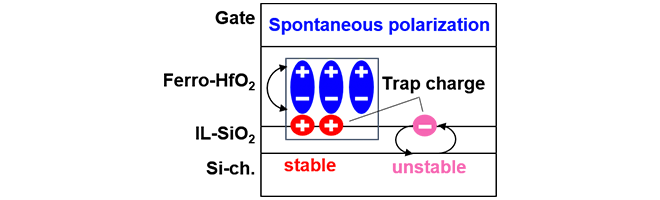

Recently, FeFET (Ferroelectric FET), an FET with a ferroelectric material as a gate insulator, has attracted much attention as an emerging memory. FeFET is a kind of non-volatile memory based on Vth (threshold voltage) modulation due to spontaneous polarization reversal in the ferroelectric layer. Particularly, a HfO2-based FeFET enables low-voltage/high-speed operation, and is compatible with CMOS process.

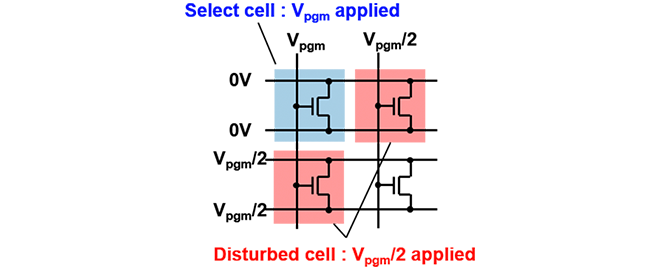

In the memory product, memory cells are arranged into an array so that multiple cells share wires for high bit density (Fig. 1). In this array architecture, when we apply program voltage to a selected cell, the cells which share the same wire will inevitably experience low voltage stress. If this low voltage stress is applied for too long period, unintentional polarization reversal (disturb) will occur. To prevent unintentional data loss by disturb, deep understanding of the polarization reversal mechanism is required.

In this work, we focused on the coupling between polarization reversal and charge trapping. We investigated the effect of charge trapping on polarization reversal dynamics in low voltage stress. Based on the experimental results, we proposed a novel operation scheme to suppress disturb. It is widely known that undesirable charge trapping also occurs in FeFET and it cancels the effect of spontaneous polarization (Fig. 2)[1]. Among them, unstable trap charges, which can be discharged immediately, will dynamically strengthen the electric field in ferroelectric layers. We conceived that to suppress trapping and to facilitate detrapping can prevent unintentional disturb.

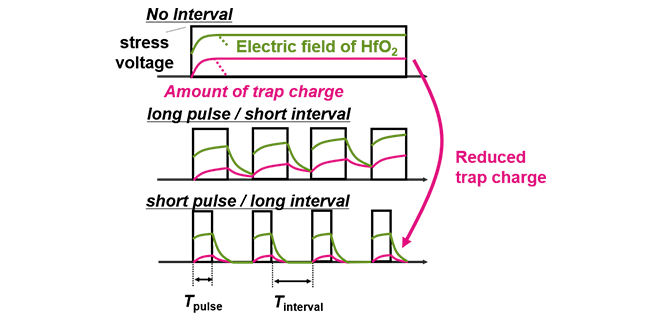

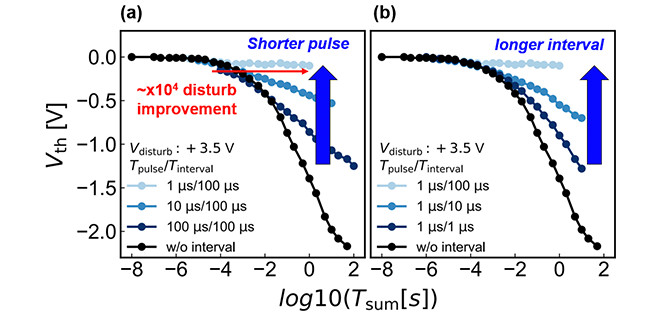

To verify this hypothesis, we used stress sequences with low voltage pulse divided by 0V interval, and investigated how the width of pulses and intervals affected polarization reversal dynamics (Fig. 3). Fig. 4(a) shows that Vth shift was suppressed by shortening pulse width and Fig. 4(b) shows that Vth shift was suppressed by lengthening interval.

Controlling the trap charges is an effective technique to suppress disturb as expected.

Based on the measurement taken this time, 1 μs pulse and 100 μs interval operation scheme showed the minimum Vth shift, and we successfully improved the disturb immunity by more than 4 orders of magnitude, measured by the sum of the pulse width by which Vth shift starts.

This article is reconstructed from an excerpt of reference[2] presented at 2023 IEEE IRPS (International Reliability Physics Symposium) in March 2023.

Reference

[1] R. Ichihara, et al., VLSI2020, TF1.2.

[2] T. Hamai, et al., IRPS2023, 6A1.