Please select your location and preferred language where available.

Accurate Picture of Cycling Degradation in HfO2-FeFET Based on Charge Trapping dynamics Revealed by Fast Charge Centroid Analysis

February 24, 2022

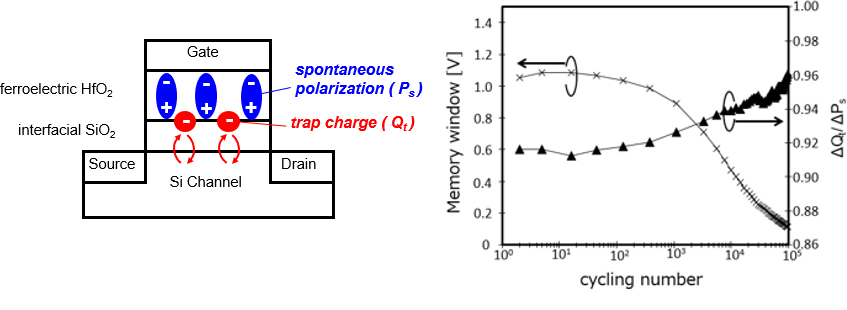

Recently, FeFET (Ferroelectric FET) which is a MIS*1 FET with ferroelectric gate insulator has attracted much attention as an emerging memory. FeFET is a non-volatile memory based on Vth modulation due to spontaneous polarization (Ps) reversal in gate insulator. In particular, HfO2-based FeFET has many advantages such as high speed/low voltage operation as well as CMOS compatibility.

About HfO2-based FeFET, we previously reported that huge amount of charge trapping/de-trapping cause undesired Vth shifts, resulting in cancellation of almost 90% of Ps effect [1,2]. This charge trapping/de-trapping also causes cycling degradation which is a key issue of HfO2-based FeFET. As shown in Fig.1[1,2], the ratio of the amount of charge trapping/de-trapping to that of spontaneous polarization reversal increases with cycling resulting in memory window reduction. However, the type of carriers causing higher charge trapping/de-trapping ratio and the degradation mechanism are still unclear.

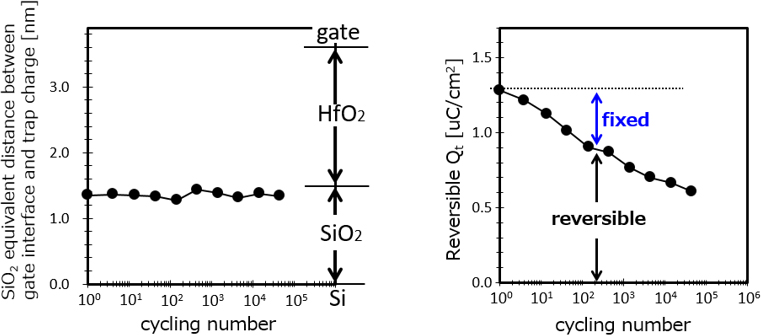

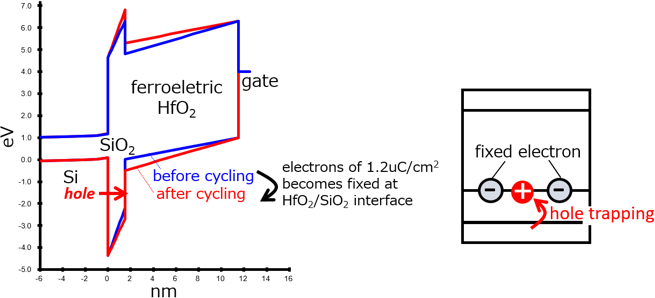

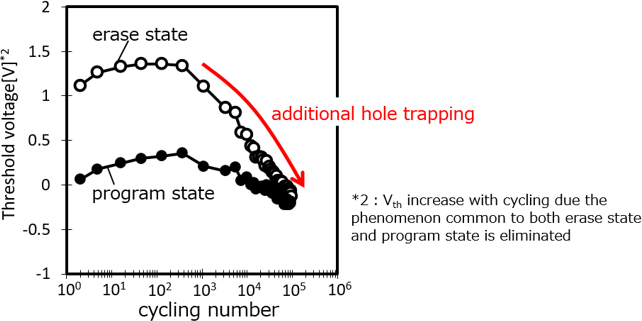

In this study, based on the method to measure the gate current due to charge trapping/de-trapping and drain current simultaneously, we successfully realized the quantitative extraction of various kinds of charge trapping/de-trapping. As a result, it is demonstrated that a part of electrons at HfO2/SiO2 interface, which is caused by program operation, becomes fixed with cycling followed by an additional hole trapping at erase operation. This trapped hole is released at next program operation, resulting in memory window reduction. Based on these findings, we conclude that not only electron trapping but also its stabilization should be suppressed for the improvement of cycling characteristic of HfO2-based FeFET.

This achievement was presented at 2021 IEEE IEDM (International Electron Devices Meeting).

This material is a partial excerpt and reconstruction of the reference [3] @ 2021 IEEE.

- Metal Insulator Semiconductor

Reference

[1] R. Ichihara et al., VLSI2020, TF1.2.

[2] M. Saitoh et al., IEDM2020, 375.

[3] R. Ichihara et al., IEDM2021, 131.