Please select your location and preferred language where available.

Study of 6bit/cell Cryogenic Operation of 3D Flash Memory

September 28, 2021

Semiconductor devices have followed Moore’s low and increased the densities utilizing state-of-the-art technologies. Since the invention of NAND Flash memory, its bit density has been increased, by the cell size scaling, the multi-level cell technology for both 2D and 3D Flash memory, and increase in the number of stacking layers of cells for 3D Flash. Multi-level cell technology requires a tight Vth distribution. It is essential to have small read noise, long data retention and high cycle endurance. Recently, with the growth of the quantum computing and high performance computing, there are increasing demands for the computer systems and electrical components that can operate at relatively low temperature. It has been reported that the characteristics of several types of semiconductor devices can be improved by cryogenic temperature[1]. This report is the first to introduce a cryogenic operation and characteristics of 3D Flash memory at 77 K immerged in the liquid nitrogen.

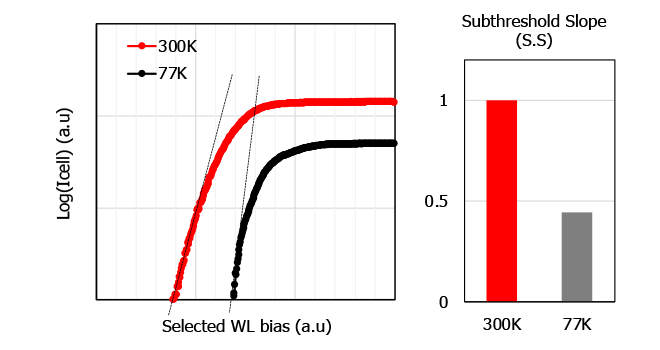

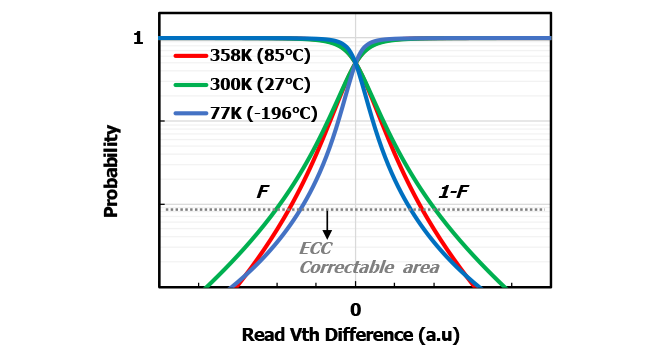

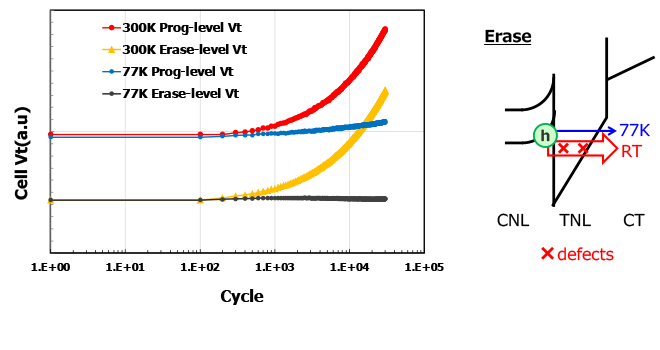

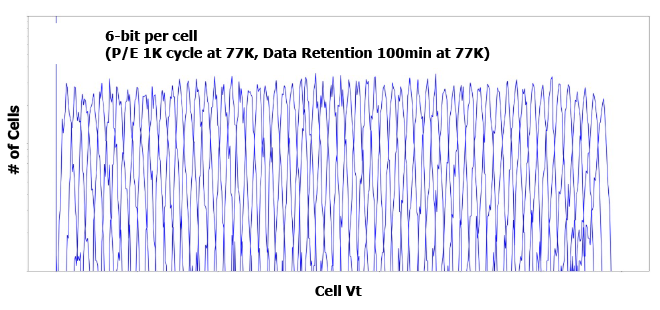

Our experiments show that not only 3D Flash memory can be operated at 77 K (-196° C), but also cryogenic operation steepens the I-V characteristics of bit cells as shown in Fig. 1. Fig. 2 shows the cumulative probability of cell Vth differences at multiple read, known as the read noise characteristic. At 77 K, the read noise characteristics is clearly improved compared to room temperature of 300 K and 358 K. Fig. 3(a) shows the cycle endurance characteristics of program/erase (P/E) cycle. The cycle endurance at 77 K is more than 10 times higher than at 300 K. At room temperature, hot holes are generated by thermal fluctuation effects, and these become the cause of defects in the tunnel oxide. On the other hand, hot holes are less generated at cryogenic temperature, and it leads to less damage. Fig. 4 shows the data retention characteristics, and it is clear that the shift of cell Vth due to the charge loss is greatly reduced at 77 K. This can be interpreted that the charge loss is caused by the thermal excitation of the trapped carriers therefore suppressed greatly at cryogenic temperature.

The read noise characteristics, the cycle endurance and the data retention characteristics were significantly improved at cryogenic temperature, and all of these improvements enable us to achieve 6-bit per cell operation as shown in Fig. 5.

(a) Vg-Id (b) Normalized Sub-threshold slope

This work was presented in the International Memory Workshop (IMW2021), in May 2021[2]. Related studies was presented in the Electron Devices Technology and Manufacturing Conference (EDTM2021) in April 2021, and received the IEEE EDTM2021 Best Paper Award[3].

This article is reconstructed from excerpts of references [2],[3] @IEEE.

[1] G.-H. Lee, D. Min, I. Byun, and J. Kim, "Cryogenic computer architecture modeling with memory-side case studies", Proceedings - International Symposium on Computer Architecture, pp. 774-787

[2] Y. Aiba, H. Tanaka, T. Maeda, K. Sawa, F. Kikushima, M. Miura, T. Fujisawa, M. Matsuo, H. Horii, H. Mukaida, and T. Sanuki, ” Bringing in cryogenics to storage: Characteristics and performance improvement of 3D flash memory”, 2021 IEEE International Memory Workshop, IMW 2021 – Proceedings 9439594

[3] Y. Aiba, H. Tanaka, T. Maeda, K. Sawa, F. Kikushima, M. Miura, T. Fujisawa, M. Matsuo, and T. Sanuki, ” Cryogenic Operation of 3D Flash Memory for New Applications and Bit Cost Scaling with 6-Bit per Cell (HLC) and beyond”, 2021 5th IEEE Electron Devices Technology and Manufacturing Conference, EDTM 2021, 9421051