Please select your location and preferred language where available.

What is CMOS directly Bonded to Array (CBA) Technology?

3D flash memory is a semiconductor device indispensable for realizing various technologies that support modern society, such as the internet of things (IoT), artificial intelligence (AI), and big data. To enable these technologies, improvements in 3D flash memory performance—such as faster operation speeds and lower power consumption—are required. Furthermore, if these demands can be met at low cost and supplied worldwide affordably, 3D flash memory can be utilized in a wider range of fields. At KIOXIA, to meet these requirements, we have developed the CMOS directly Bonded to Array (CBA) technology and achieved mass production, which we will introduce here.

What is CBA Technology?

3D flash memory has a structure in which memory cells, traditionally formed in a two-dimensional layout, are stacked vertically.

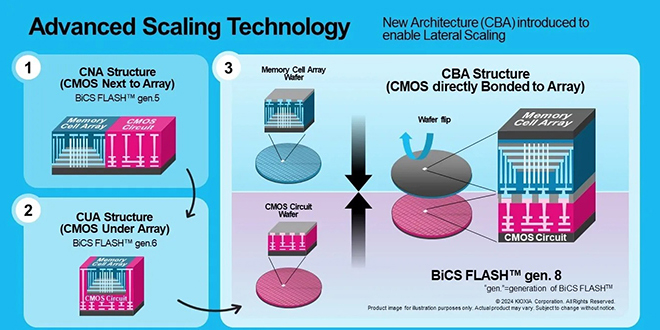

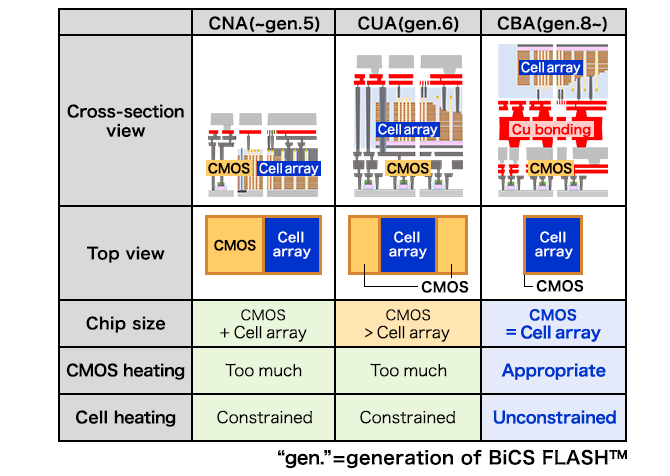

Table 1 shows a comparison of the generational structures of KIOXIA’s 3D flash memory BiCS FLASH™. The structure of 3D flash memory is broadly divided into the memory cell array region (hereafter “cell array”), which stores information, and the CMOS circuit region (hereafter “CMOS”), which operates the cell array. Up to BiCS FLASH™ generation 5 (hereafter referred to as “BiCS FLASH™ gen.”), the CMOS Next to Array (CNA) structure was adopted. In the CNA structure, CMOS is formed beside the cell array, so the chip size is approximately the sum of the CMOS and cell array sizes. Also, since the cell array is formed after CMOS, the CMOS is exposed to high-temperature heat during cell array formation. This high temperature degrades CMOS characteristics, so the heat during cell array formation had to be limited to the minimum temperature that maintains cell characteristics.

One way to reduce the cost of 3D flash memory is to reduce chip size to obtain more chips from a 300 mm wafer. Therefore, BiCS FLASH™ gen. 6 introduced the CMOS Under Array (CUA) structure, where CMOS is formed beneath the cell array. The CUA structure allows chip size reduction by forming the cell array continuously on top of CMOS on a single Si wafer. However, like CNA, the temperature during CMOS and cell array formation is limited, creating a trade-off between improving cell and CMOS performance, making it difficult to achieve both simultaneously.

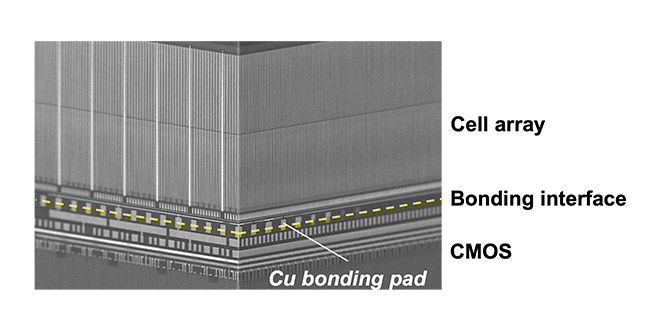

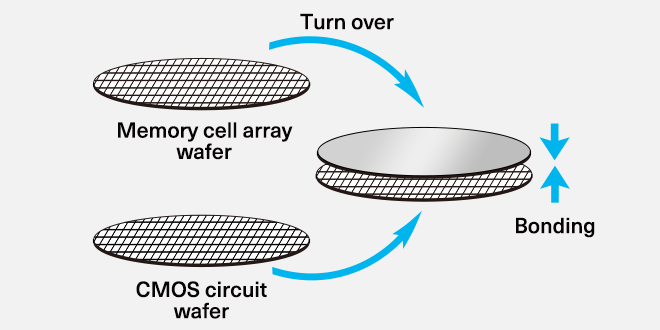

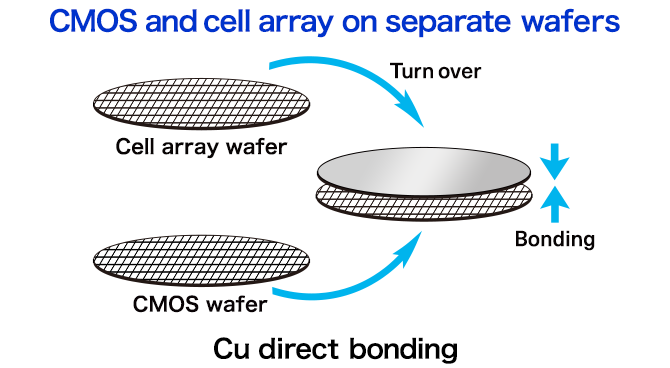

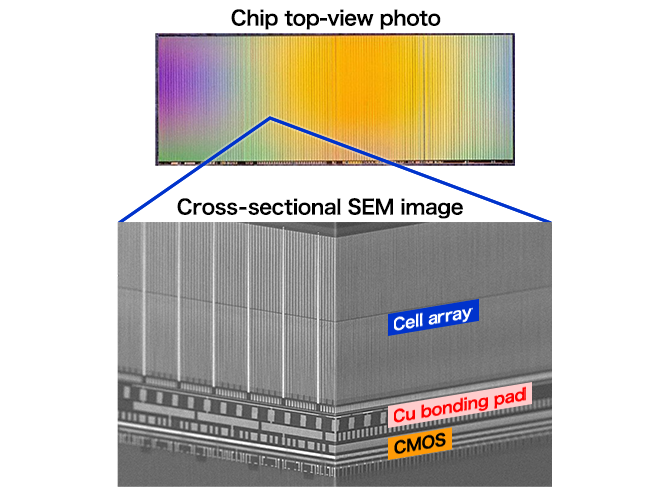

The proposed solution is the CBA structure. In the CBA structure, CMOS and the cell array are formed on separate Si wafers, each with copper (Cu) bonding pads formed on their surfaces. Then, as shown in Fig.1, the Si wafers are bonded together using a Cu direct bonding process, electrically connecting CMOS and the cell array via the Cu bonding pads to form the 3D flash memory. As a result, by stacking CMOS and the cell array, chip size is reduced while allowing optimal thermal processes for both CMOS and the cell array, enabling performance improvements.

Two key technologies enable the realization of the CBA structure.

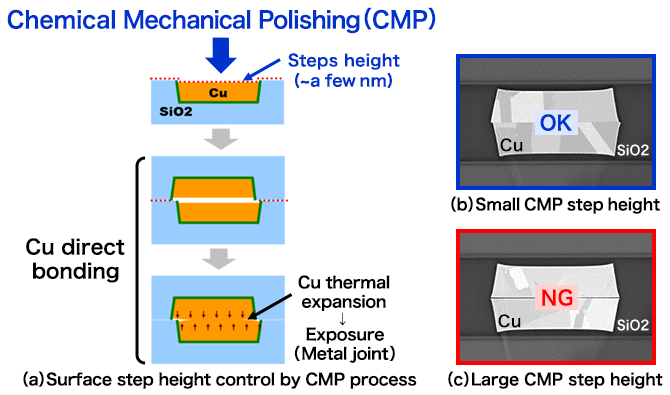

First is the Cu bonding pad step height reduction technology. As mentioned, the CBA structure requires gapless bonding of both Cu bonding pads and SiO2 interlayer films using the Cu direct bonding process. Therefore, as shown in Fig.2(a), the step height between the Cu bonding pads and SiO2 interlayer films formed on the surfaces of the CMOS and cell array wafers must be suppressed to the nanometer level.

This extremely fine step height control is achieved by the chemical mechanical polishing (CMP) process. Polishing the surface of a 300 mm wafer by CMP to achieve a step height of a few nanometers is akin to controlling morphology with the precision of reducing a step to less than the thickness of a single sheet of copy paper inside the Tokyo Dome. After bonding the CMOS and cell array wafers with such nanometer-level surface step control face-to-face at the SiO2 interlayer film surfaces, annealing causes thermal expansion of Cu, resulting in metallic bonding between Cu pads and enabling electrical connection. When the step height is small, as in Fig.2(b), the Cu pads on the upper and lower sides connect without gaps. Conversely, if the step height is large, as in Fig.2(c), gaps form between the Cu pads, preventing electrical connection. Since millions of Cu bonding pads connect CMOS and the cell array, the CBA structure requires extremely high CMP process control.

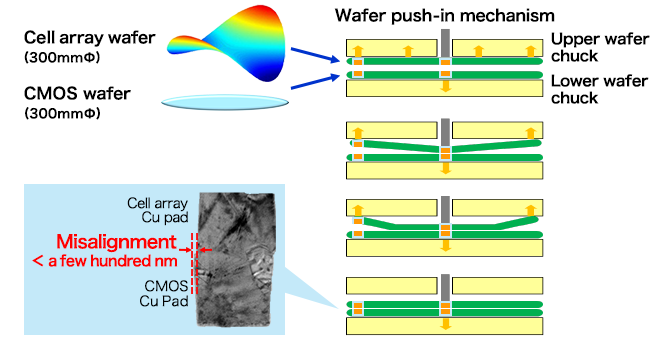

The second key technology is the alignment technology between the upper and lower wafers in the Cu direct bonding process. Fig.3 shows the sequence of the Cu direct bonding process. In this process, the surfaces of the CMOS wafer and the cell array wafer are faced together and gradually brought closer from the center to the outer edge of the wafer. To electrically connect CMOS and the cell array from the center to the outermost edge of a 300 mm wafer, wafer positioning must be controlled within a few hundred nanometers or less. Furthermore, as shown in Table 1, the cell array wafer contains numerous memory cells and word lines, resulting in very large and complex stresses. Consequently, as shown in Fig.3, the cell array wafer exhibits a complex warp shape resembling a potato chip.

This warped cell array wafer is bonded to the nearly flat CMOS wafer with a positional deviation of only a few hundred nanometers or less. This precision is comparable to repeatedly landing a golf ball hit 200 yards within just a few millimeters of the pin. This demonstrates the extremely high process control of the Cu direct bonding process in the CBA structure.

Production and Future Prospects of the CBA Structure

By achieving such highly advanced process control, the CBA structure was applied in the BiCS FLASH™ gen. 8 products. Fig.4 shows a top-view photo and cross-sectional SEM image of the chip, confirming that CMOS and the cell array are connected by numerous Cu bonding pads. By separately forming CMOS and the cell array and bonding them via Cu bonding pads, cell current improved by 35% compared to the previous generation, and interface speed reached 3.6 Gbps [1][2].

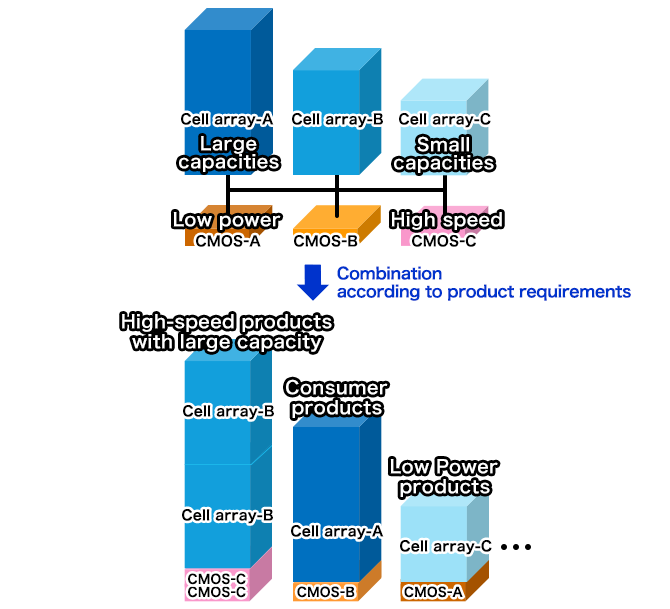

Moreover, the CBA structure is highly effective in meeting diverse product demands for the future of 3D flash memory. Fig.5 shows the product image of future CBA structure post BiCS FLASH™ gen. 9. By combining CMOS with different performance levels and cell arrays with different capacities, it becomes possible to realize 3D flash memory that supports the evolution of IoT, AI, big data, and other technologies.

Reference

[1] M. Tagami, "CMOS Directly Bonded to Array (CBA) Technology for Future 3D Flash Memory," in Proc. 2023 IEEE International Electron Device Meeting (IEDM).,19-5.

[2] S. Kobayashi et al., "High Performance 3D Flash Memory with 3.2Gbps Interface and 205MB/s Program Throughput based on CBA (CMOS Directly Bonded to Array) Technology," in Proc. 2023 IEEE International Electron Device Meeting (IEDM).,35-2.