Please select your location and preferred language where available.

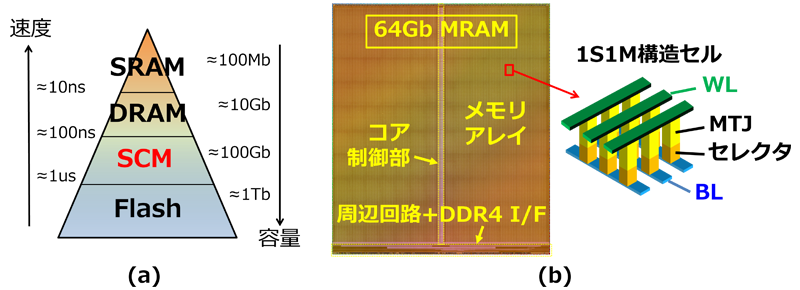

AI等の新たなアプリケーションの需要の高まりから、大容量・高速動作を実現するストレージクラスメモリ(SCM)の導入が期待されています(図1(a))。磁気抵抗メモリ素子(MTJ)を用いた磁気メモリ(MRAM)は高速性と高信頼性からSCMの有力な候補の一つと考えられていますが、これまでSCMとして求められるメモリ容量に到達することができていませんでした[1]。今回MTJと選択素子(セレクタ)を直列に接続した1S1M構造セルを採用する事で、高密度(4F2)のセルアレイを実現し[2-3]、64ギガビットMRAMチップ(図1(b))を開発しました。

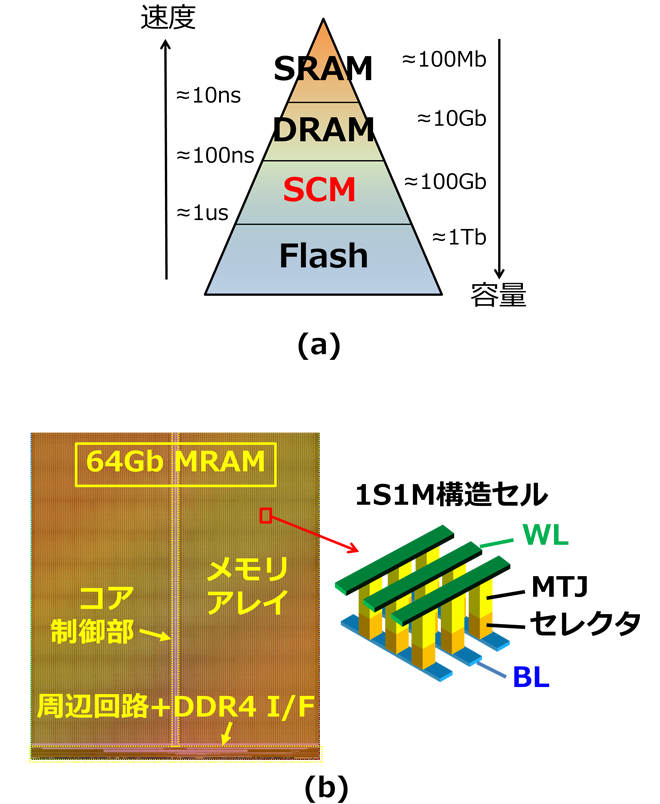

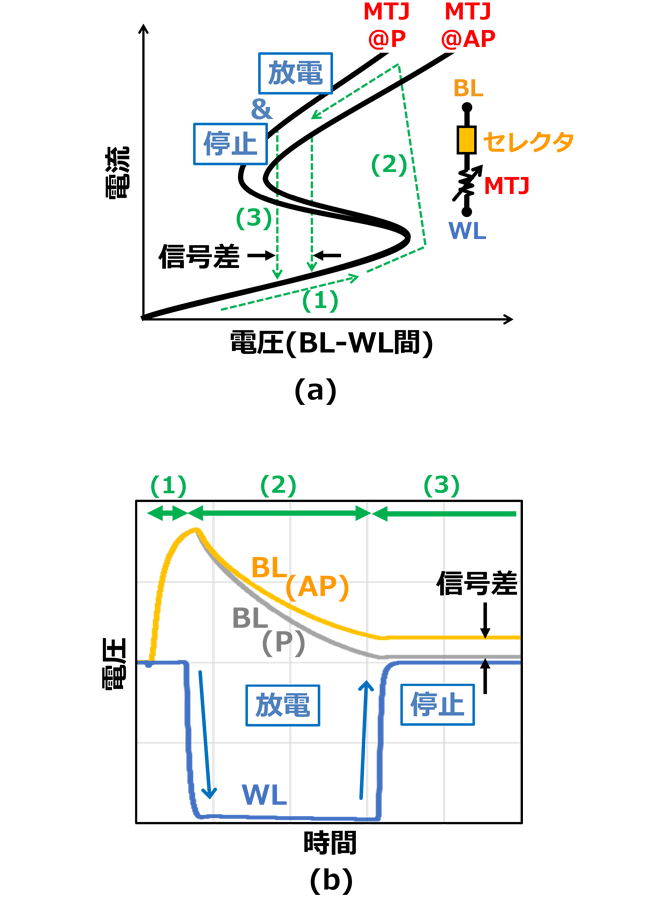

MTJは低抵抗(P)状態と高抵抗(AP)状態を持つ抵抗変化型のメモリ素子で、セレクタはオン/オフ状態を持つスイッチとして機能します(図2)。通常、抵抗変化型のメモリは、ある電流(または電圧)を印加して得られる電圧(または電流)を検知することで読出しを実現します。しかし、メモリサイズが小さい1S1M構造セルにおいて同様の印加方法で読出しを行うことは困難であることがわかっています。その理由は、読出しと書込みが同じパスであることから、読出し中に書込み(読出しディスターブ)が起きやすいためです。セルサイズを小さくすると、さらに起こりやすくなります。それを避けるために電流を制限すると、得られる信号量が小さくなったり、セレクタのオン/オフの繰り返し(発振)が発生したりしてしまい、読出しの信頼性が低くなります。このことから、1S1M構成のMRAMメモリセルの読出し方法として、新たな手法が必要となります。

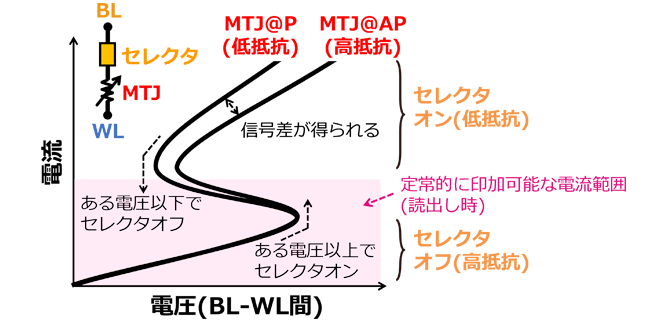

新規に提案した時間制御放電読出し技術は、セレクタのオン時間を短く制御することで、セル電流を小さく短時間に抑えながら、充電した電荷を放電して読み出す方式で、既存課題の読出しディスターブや発振を抑制する手法です(図3)。ビット線(BL)に一定の電圧を充電した後、ワード線(WL)の電圧を下げることで、セレクタがオンになり、BLに充電していた電圧を放電します。BLの電位はセレクタがオフ状態に遷移した時点で一定の電圧を保持するため、この電圧を取得することでMTJに流れる電流を最低限にして状態を読み出すことができます。

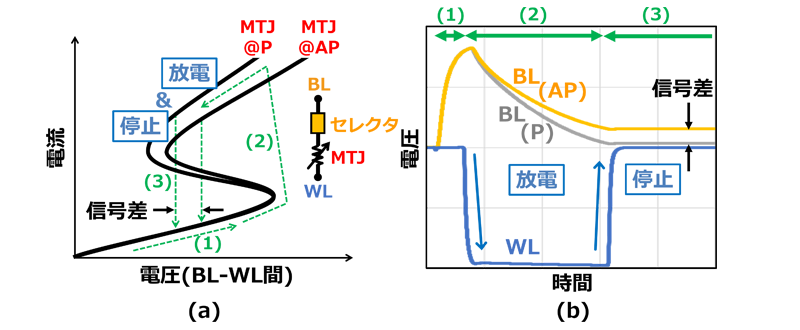

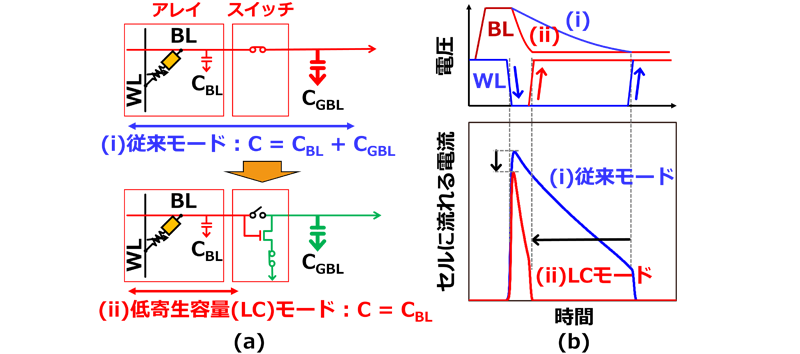

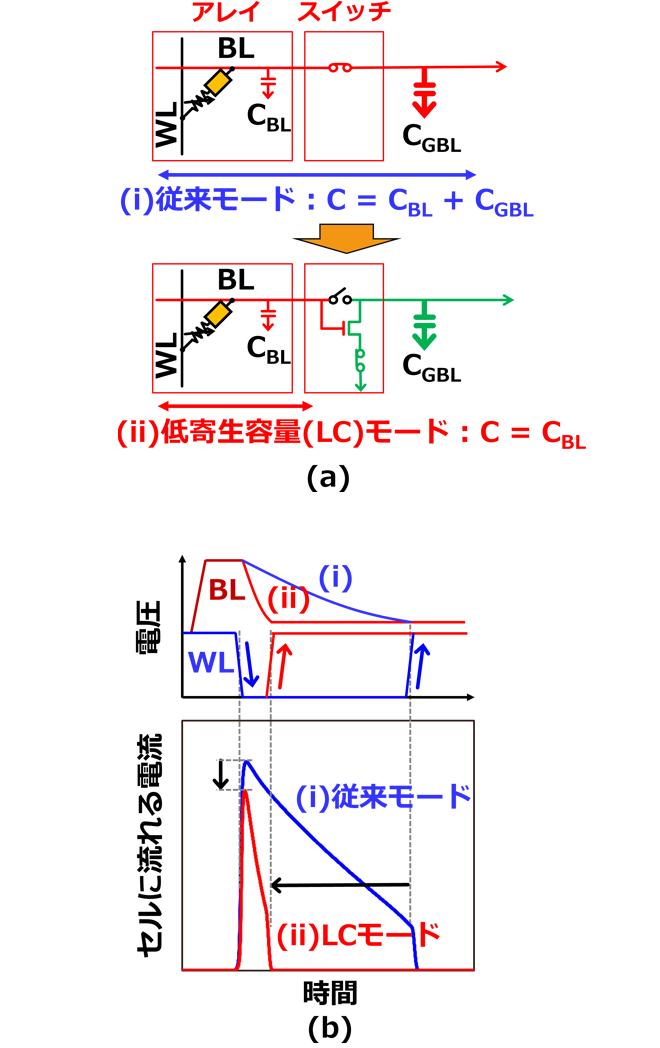

さらなる読出しディスターブ対策として、BLの容量を削減する低寄生容量モード(LCモード)を提案しました(図4)。これはセレクタがオフ状態に遷移した時点の電圧をトランジスタのゲートで受ける事で、メモリセルに接続するBLの寄生容量を最低限とする方式で、メモリセルに流れる電流の削減の他、放電時間の削減による高速化が期待できます。

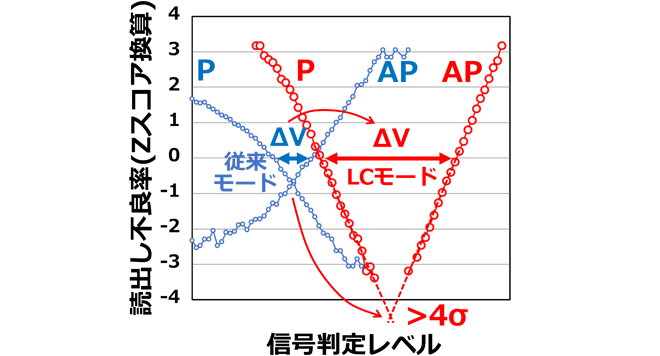

64ギガビットMRAMチップ上でMTJのP状態/AP状態それぞれに、数nsという高速な読出しパルスを印加した際の読出し信号分布の測定結果を図5に示しました。LCモードを利用することで、期待通りのP状態<AP状態が-4σ以上保持できており(不良率10ppmレベル以下)、実用レベルの高い読出し信頼性が得られることを実証しました。

今回の成果は、これまでMRAMでは介入できていなかったSCM領域(図1(a))への進出の可能性を示しています。今後AIやCXLシステムなどの新たな市場においてMRAMが活用されることが期待されます。

本成果は2025年2月に開催されたISSCC2025において発表されました。

文献

[1] K. Rho et al., “A 4Gb LPDDR2 STT-MRAM with compact 9F2 1T1MTJ cell and hierarchical bitline architecture”, ISSCC, pp. 396-397, 2017.

[2] S. M. Seo et al., “First demonstration of full integration and characterization of 4F2 1S1M cells with 45 nm of pitch and 20 nm of MTJ size”, IEDM, pp. 218-221, 2022.

[3] H. Aikawa et al, “Reliable memory operation with low read disturb rate in the world smallest 1Selector-1MTJ cell for 64 Gb cross-point MRAM”, IEDM, pp. 20.1.1-20.1.4, 2024.

[4] K. Hatsuda et al., “A 64Gb DDR4 STT-MRAM Using a Time-Controlled Discharge-Reading Scheme for a .001681um 1T-1MTJ Cross-Point Cell”, ISSCC, pp. 30.6.1-30.6.4, 2025.