Please select your location and preferred language where available.

大容量化への道を切り拓く革新的技術

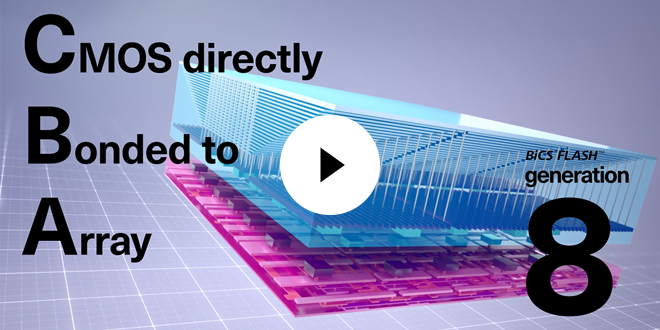

BiCS FLASH™ 製品における大きな進化の背景には、いくつかの画期的なイノベーションがあります。密度、性能、電力効率の向上は、フラッシュメモリの設計および組み立て工程の進化によって実現されています。CMOS directly Bonded to Array(CBA)技術、On Pitch Select Gate(OPS)技術、32枚積層技術が3次元フラッシュメモリの未来をどのように切り拓いているかをご紹介します。

前工程における技術

インタビュー

2枚のウエハーを高精度に貼り合わせて高密度化 ストレージに新たな価値をもたらす3次元フラッシュメモリ

近年、メモリセルを“高層化”して記憶密度を高める技術の開発は、各フラッシュメモリメーカーで特に活発になっている。新しい世代のフラッシュメモリが発表されるたびに層数が増え、200層を超える製品もある。ただし、キオクシアのメモリ事業部長である井上敦史氏は、「メモリセルの“高層化”は、あくまでも大容量化や記憶密度向上の一つの方法であって、われわれは積層数の増加のみにこだわっていない」と語る。

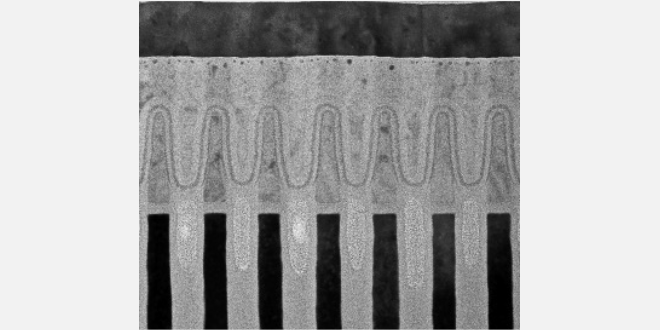

OPS技術

従来はメモリセルとして使われない「ダミー」部分が配置されていましたが、 OPS技術では、これらの不要な部分を削減し、実際にデータを記録できる領域を増やすことで、メモリの密度を大幅に向上させています。

後工程における組立技術

インタビュー

「わずか2mm」に込められた大容量フラッシュメモリの革新技術

AIの進化を後工程で支える

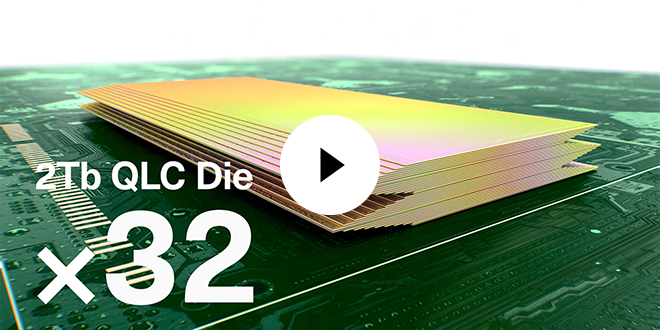

メモリチップ32枚を1パッケージに積層

AIの急速な普及により、フラッシュメモリではさらなる大容量化が求められている。キオクシアは、高さ2mmにも満たないパッケージに、32枚の2Tb(テラビット)メモリチップを積層し、8TB(テラバイト)という大容量フラッシュメモリの開発に成功。それを支えているのが、ウエハーを極限まで薄く削る加工技術をはじめとする、高度な後工程技術である。

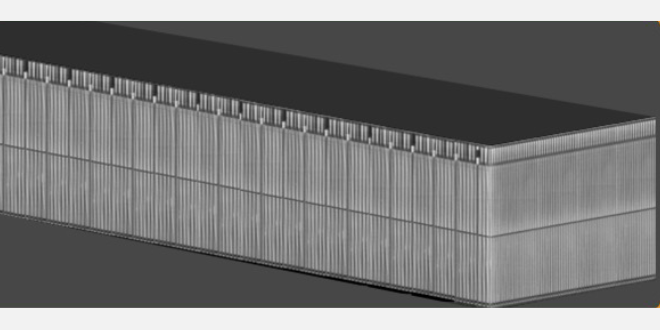

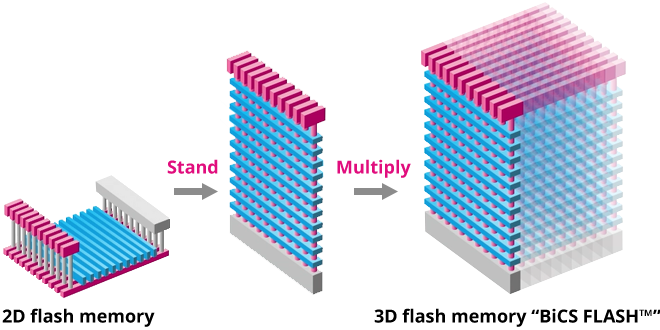

全世代に共通するBiCS FLASH™ 技術の基礎要素

3次元フラッシュメモリ「BiCS FLASH™」は、メモリセルを垂直方向に積層することで、ストレージ密度を大幅に高めています。この高層ビルのようなアーキテクチャは、メモリセルを並べて配置する平面構造のフラッシュメモリの限界を克服します。セル間の距離を広げることで、セル同士の干渉を低減し、平面構造のフラッシュメモリと比べて、密度、性能、電力効率の向上を実現しています。

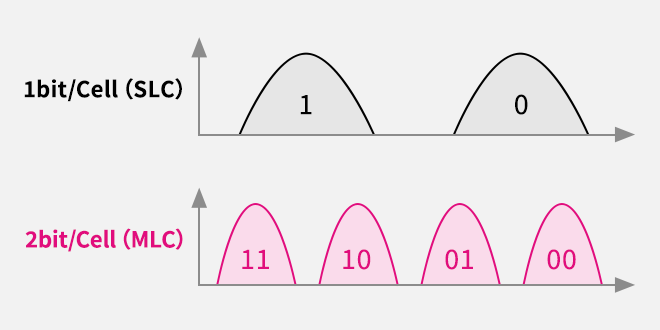

TLC(トリプルレベルセル)とQLC(クワッドレベルセル)技術

3次元フラッシュメモリ「BiCS FLASH™」の製品ラインナップには、3ビット/セル(TLC)と4ビット/セル(QLC)製品が存在します。QLC技術は、メモリセルごとのデータビット数を3から4に増やすことで、容量を大幅に拡大し、2テラビット(Tb)ダイを16層積層する構造で4テラバイト(TB)という大容量をシングルパッケージで実現しました。

キオクシアは、SLCからMLCへ、MLCからTLC、そしてTLCからQLCの開発を推進してきたメモリメーカーです。

キオクシアのQLC技術は、高密度で低コストのストレージソリューションを必要とするアプリケーションに適しています。QLCは、フットプリントを削減した高密度単一パッケージでストレージソリューションを拡張します。

用途別に製品を見たい方

車載機器、小型高性能PC、クラウドサーバーやハイパースケールデータセンター用途などに高性能、大容量、低消費電力、低遅延、高信頼性で応える当社のメモリとストレージソリューションは、新しいアプリケーション開発を支え様々な技術・製品の潜在能力を引き出します。

サポート情報

法人向け製品(メモリ・SSD・SDメモリカード)に関する技術的なご質問、各種資料請求、サンプル・ご購入などは、こちらからお問い合わせください。