Please select your location and preferred language where available.

BiCS FLASH™ 第8世代は、CBA(CMOS directly Bonded to Array)技術を採用しました[1]。これはCMOS回路とメモリアレイを別々のシリコンウエハーに形成したのち、それら2枚のウエハーを貼り合わせる技術です。この技術により動作速度の向上とチップサイズの縮小という二つの効果を得られました。動作速度の向上は、CMOS回路とメモリアレイ形成時の熱処理プロセスが個別に最適化されることによってもたらされます。今回は、二つ目の効果であるチップサイズの縮小に寄与したCBL(Crossed Bit Line)アーキテクチャを中心に、CBL導入に伴うセンスアンプ動作マージン改善技術と、OPS(On Pitch SGD)導入によって得られる効果について、概要を紹介します[2]。

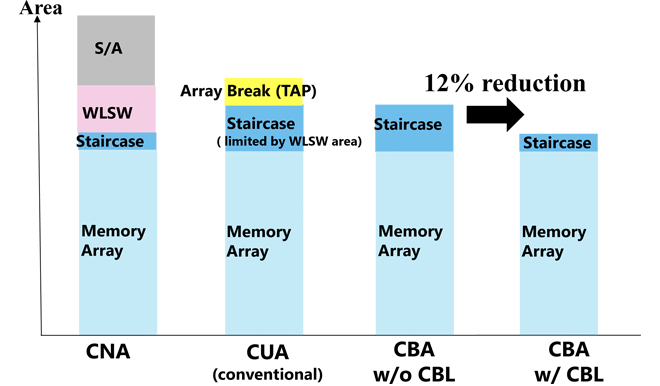

従来のCUA(CMOS Under Array)構造ではメモリアレイの上方にBL(Bit Line)が配置され、BL制御回路であるS/A(Sense Amplifier)はメモリアレイの下方に配置されていました。そのためBLをS/Aに接続するためのコンタクトを配置するTAPと呼ばれる領域が必要でした。一方CBA構造では、メモリアレイチップ側に配置されるBLと、CMOSチップ側に配置されるS/Aとがウエハーを貼り合わせた後に互いに向き合う形になります。したがって、BLとS/A間の接続に対してTAP領域を設けることが不要となりチップサイズ縮小を実現できます(図1)。

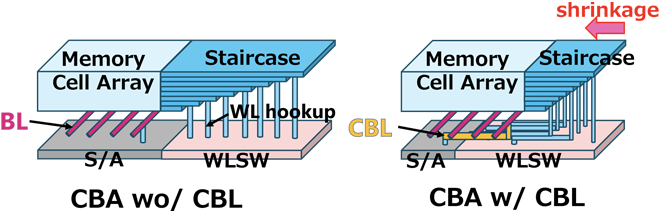

次に、Staircaseと呼ぶWL(Word Line)引き出し領域の面積削減について説明します。WLのドライバ回路であるWLSW(Word Line Switch)はトランジスタ性能と素子間耐圧を確保する必要があり、通常はStaircase幅よりもWLSW幅の方が広くなります。従来のアーキテクチャではS/Aの幅はメモリアレイの幅と一致していたので、Staircaseの外側にWLSWがはみ出してしまいます。つまりWL引き出しのためにStaircaseをWLSWの幅まで拡大する必要がありました。これはチップサイズ、最終的にはコストの増大に繋がります。そこで図2に示すように、S/Aをメモリアレイ幅よりも縮小しWLSWをメモリアレイ下に押し込みます。するとStaircaseを本来の幅で形成できるため、チップサイズが縮小できます。ところがこれではS/Aと対応するBLの位置関係がずれてしまうという新たな問題が発生します。そこでCBLと呼ぶBLに直交する方向の配線を使い、端のBLから順に対応するS/Aの位置までBLを引き込むことでこの問題を解決しました。

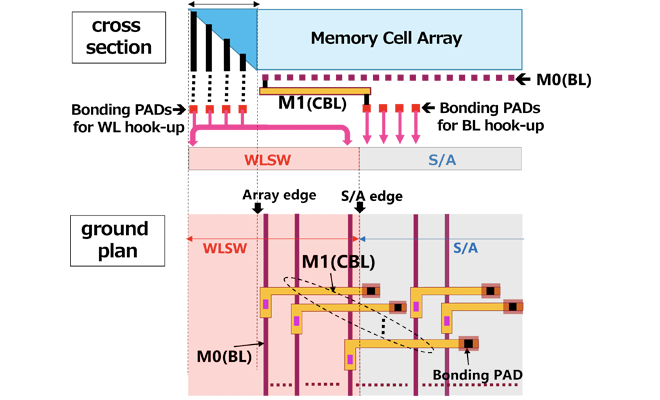

メモリアレイチップ内でS/Aの位置まで引き込んだCBL配線は、貼合パッドを介してCMOSチップ側のS/Aに接続されます。またWLSWの一部がメモリアレイ下に配置されるのでWLSWからStaircaseまでの接続用の配線が混雑してしまいます。この問題を解決するために、CMOSチップ側の三層の配線層を使って結線することですべてのWLSWをStaircaseとメモリアレイの下に配置することに成功しました(図3)。

このCBLアーキテクチャの採用によりS/AやWLSWの配置を最適化し、Staircaseの幅を縮小することができました。これによりBiCS FLASH™ 第8世代において12%のチップサイズ縮小を達成しました[2](図1)。

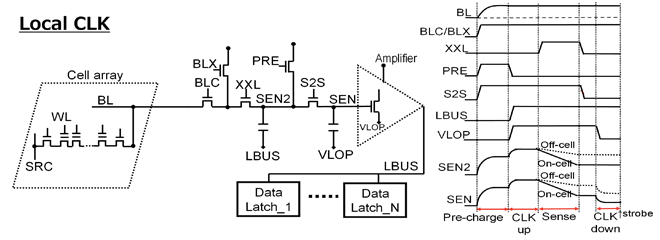

CBLアーキテクチャを採用しWLSWをStaircaseとメモリアレイの下に配置するためにはS/A領域の縮小が必要です。S/A領域の縮小によりレイアウト可能な配線本数が減少すると、センスノードに使う配線間容量を確保することが困難となりS/Aの動作マージンが低下します。この問題を解決するためにLocal CLKという回路動作を導入しました。センスノードをSENとSEN2の二つに分割しそれぞれをVLOPとLBUSという別々の信号と容量結合させます。これらの信号を適切なタイミングで制御することで、少ない配線本数でも十分な動作マージンの確保を実現しています。

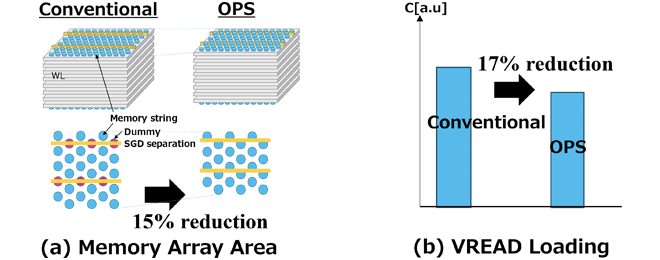

「BiCS FLASH™ 第8世代適用新技術の紹介」で紹介されているように、メモリセルとして機能しないダミーメモリストリングを削除するOPS技術も採用しています。これによりメモリアレイ面積を15%縮小しました(図5(a))。加えて、非選択WLの負荷容量が17%削減されることで(図5(b))、読み出し時間を1μs短縮し、読み出し電流を4%低減しました。

これまでに紹介してきたように、CBLアーキテクチャやOPS技術は、3次元フラッシュメモリにおいて記憶密度の向上と低コスト化を継続して進めるために有効な手法と言えます。当社はこれらの技術を今後の製品にも適用し、性能向上に役立てるとともに、より記憶密度の高い製品を開発してまいります。

本成果は2025年5月に開催されたIMW2025(International Memory Workshop 2025)において発表されました。

文献

[1] S. Kobayashi et al., “High Performance 3D Flash Memory with 3.2Gbps Interface and 205MB/s Program Throughput based on CBA(CMOS Directly Bonded to Array) Technology”, IEEE International Electron Devices Meeting (IEDM), Dec. 2023, 35-2.

[2] H.Maejima et al., “Crossed Bit Line (CBL) Architecture in 3D Flash Memory CMOS Directly Bonded to Array (CBA) Structure”, IEEE International Memory Workshop (IMW), pp.25-28, May.2025.