Please select your location and preferred language where available.

56GbpsのPAM4信号に対応したトランシーバーを開発

― NANDフラッシュメモリモジュールの広帯域化により、産業のスマート化に貢献 ―

- 2022年10月 4日

- NEDO(国立研究開発法人新エネルギー・産業技術総合開発機構)

- キオクシア株式会社

NEDOが進める「ポスト5G情報通信システム基盤強化研究開発事業」において、キオクシア株式会社は56GbpsのPAM4信号を送受信できるトランシーバーを開発し、その動作実証に成功しました。

データ通信の伝送容量を拡張するため、近年データセンターなどではPAM4方式(4値のデータ転送方式)の高速通信が採用され始めています。一方で、トランシーバーがクロック信号(回路の動作タイミングの基準となる信号)を正しく抽出できず、受信性能が大きく劣化するという課題がありました。今回、このクロックの誤認識を回避する技術を開発し、試作したトランシーバーでの動作実証に成功しました。

今後、NANDフラッシュメモリとメモリコントローラー間のインターフェースに本技術を活用することで、広帯域・大容量のメモリモジュールの実現が可能となります。本メモリモジュールを実装したMobile Edge Computing(MEC)サーバーを第5世代移動通信(5G)ネットワーク内に設置し、ビッグデータ解析を行うことで、IoTをはじめとする産業のスマート化が期待されます。

なお本成果は、IEEEのSolid-State Circuits Society(SSCS)が主催する国際会議「ESSCIRC(European Solid-State Circuits Conference、期間:2022年9月19日~22日)」に採択され、キオクシア株式会社が現地時間の9月22日に発表しました。

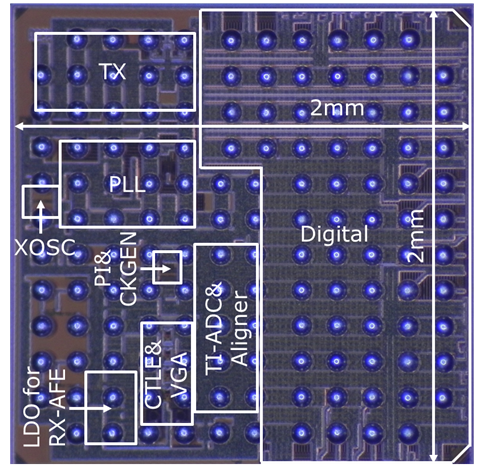

図1 今回試作したトランシーバーのチップ写真(16nm-FinFETプロセスで試作) ©2022 IEEE (※7)

1.概要

近年の第5世代移動通信(5G)やIoTの普及により、データ通信のさらなる高速化が求められています。これに伴い、そのインフラであるデータセンターなどでは、伝送容量を拡張するため、伝送方式として従来のNRZ※1方式に代わりPAM4※2方式が採用されるようになってきました。また、受信データに含まれるタイミング情報(クロック)とデータを分離するために利用するクロック・データ・リカバリ(CDR)※3も、従来は変調レート※4の2倍のクロック信号が用いられてきましたが、消費電力が大きくなるという課題を解消するため、変調レートと同じ速度のクロックを用いるCDRの採用が広がりつつあります。しかしながら、このCDRでPAM4の信号を受信すると、データを誤認することによりクロック信号を正しく抽出できず、データの判別ができない状況が発生することがあり、PAM4トランシーバーの受信性能が大きく劣化するという課題がありました。

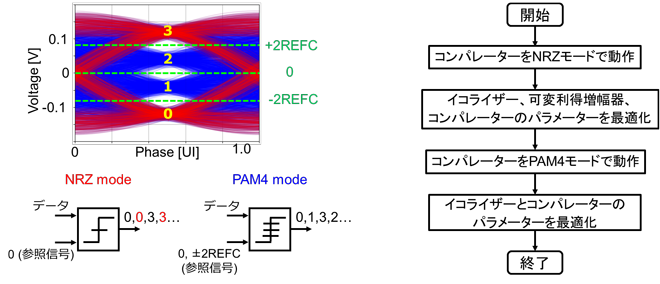

こうした背景のもと、NEDO(国立研究開発法人新エネルギー・産業技術総合開発機構)とキオクシア株式会社は、「ポスト5G情報通信システム基盤強化研究開発事業/広帯域大容量フラッシュメモリモジュールの研究開発」(以下、本NEDO事業)において、コンパレーター※5をNRZモードで動作させることにより、クロック信号を正しく抽出し、その後、PAM4モードに移行することによって毎秒56ギガビット(56Gbps)※6のPAM4信号を送受信できるトランシーバーを開発、その実証に成功しました。

なお本成果は、IEEEのSolid-State Circuits Society(SSCS)が主催する国際会議「ESSCIRC(European Solid-State Circuits Conference、期間:2022年9月19日~22日 開催地:伊ミラノ市)」に採択され、キオクシア株式会社が現地時間の9月22日に発表しました※7。

2.今回の成果

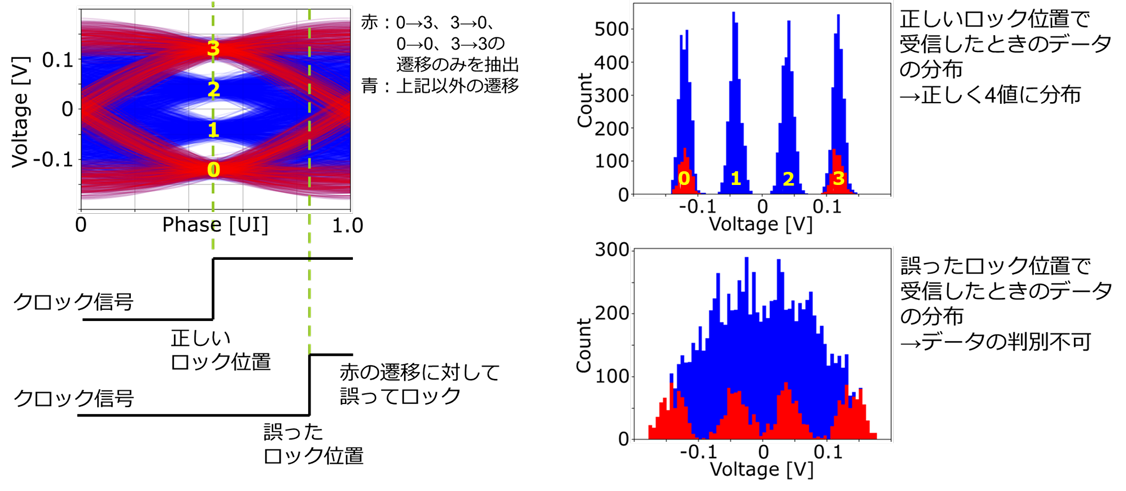

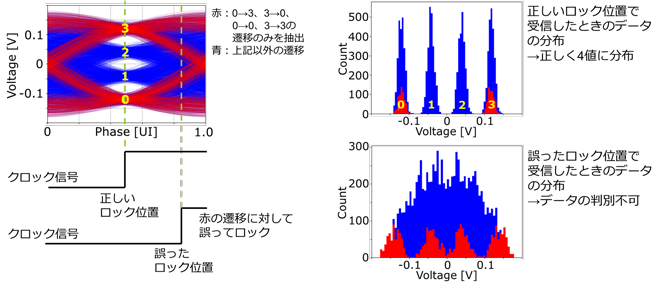

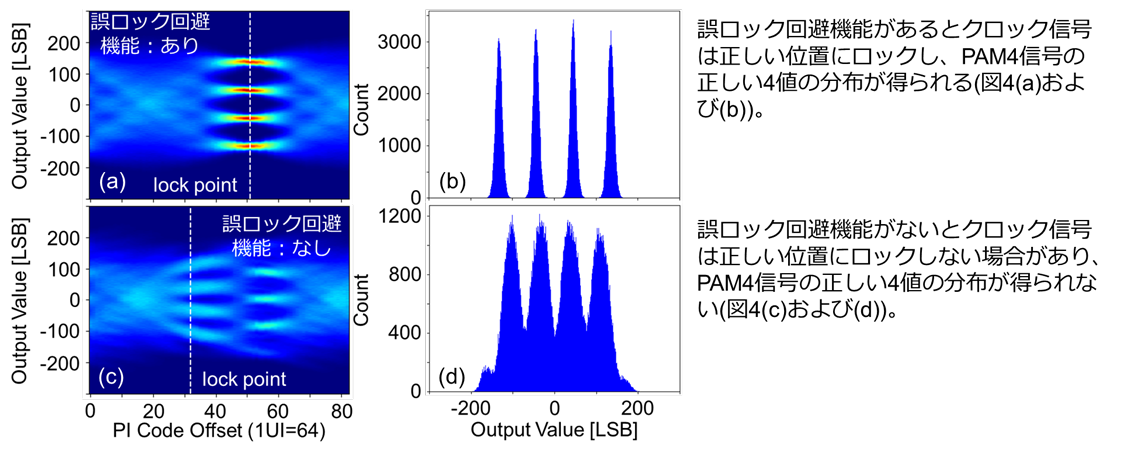

従来のCDRでは、PAM4信号からクロック信号のロック位置を決定する際、PAM4信号の特定の遷移点(0→3、3→0、0→0、3→3)だけを受信データと誤認することで、クロック信号が誤った位置にロックしてしまい、正しくデータが受信できない状況が発生していました(図2)。

図2 ロック位置の違いによるデータ受信成否 ©2022 IEEE (※7)

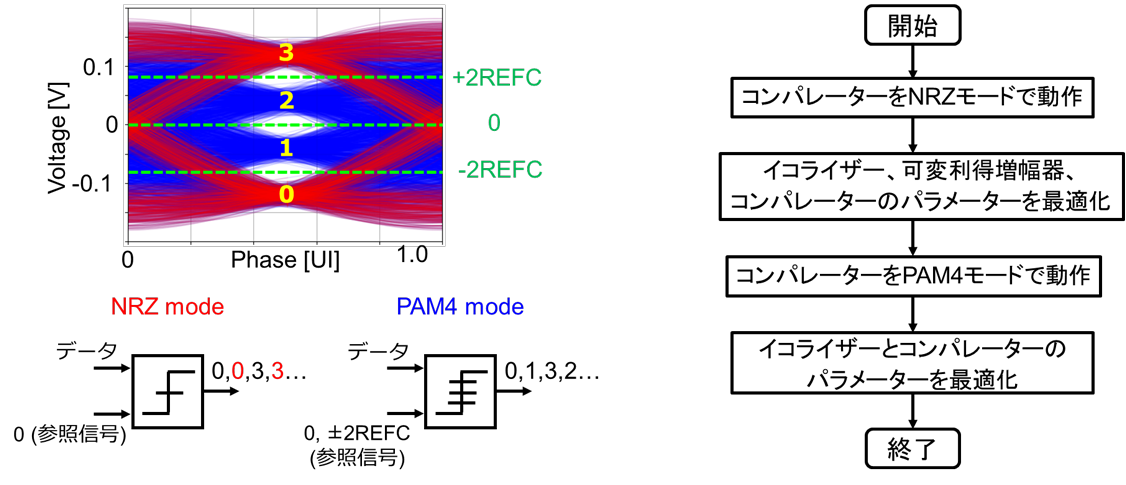

NEDOとキオクシア株式会社は、受信信号からクロック信号のロック位置を検出するにあたり、コンパレーターをNRZモードで動作させることにより特定の遷移点を見て受信データを誤認することがなくなり、誤ロックが回避できることを発見しました。これを利用して、まずコンパレーターをNRZモードで動作させてクロック信号を正しい位置でロックさせた後、コンパレーターをPAM4モードへ変更することによりPAM4信号を正しく受信することが可能となりました(図3)。具体的には、最初にコンパレーターをNRZモードで動作させた際は、受信機のイコライザー、可変利得増幅器、コンパレーターのパラメーターを最適化する制御を行い、クロック信号を正しい位置でロックさせます。コンパレーターをPAM4モードに切り替えた後にも、イコライザーおよびコンパレーターのパラメーターを最適化する制御を行うことによって、最適な位置にクロック信号をロックさせます。

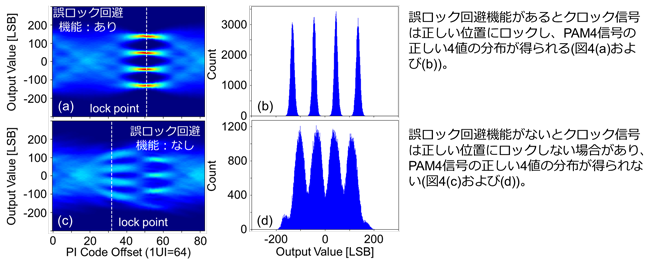

試作したトランシーバーの性能評価の際は、トランシーバーの送信機で生成した56GbpsのPAM4信号を一度チップの外部に取り出し、ケーブルを用いてチップ内の受信機にループバックすることにより、56Gbpsでの動作を確認しました。試作したトランシーバーにおいて今回考案した誤ロック回避機能の有効性を確認しました(図4)。

図3 誤ロックを回避するためのシーケンス

図4 誤ロック回避技術の有効性を確認した実験結果 ©2022 IEEE (※7)

3.今後の予定

キオクシア株式会社は本NEDO事業で研究開発中のメモリデイジーチェーン技術※8に今回の成果を活用し、広帯域大容量フラッシュメモリモジュールの研究開発を進め、消費電力40W以下、容量5TB以上、帯域64GB/s以上のメモリモジュールの実現を目指します。

これにより、5Gネットワーク内に設置した、本メモリモジュールを実装したMobile Edge Computing(MEC)サーバー※9におけるビッグデータ解析が可能となり、IoTをはじめとする産業のスマート化が期待されます。

【注釈】

- NRZ

非ゼロ復帰方式(Non Return to Zero)の略称で、1ビットのデータ(0,1)を2つのアナログレベルのパルス信号として伝送する方式です。 - PAM4

4値パルス変調方式(Pulse Amplitude Modulation 4)の略称で、2ビットのデータ(00,01,10,11)を4つのアナログレベルのパルス信号として伝送する方式で、NRZと比較して情報量が2倍となります。 - クロック・データ・リカバリ(CDR)

受信したデータ列からクロックやデータを抽出する回路です。 - 変調レート

1秒間に何回変調するかを示す値で、シンボルレート、ボーレートとも呼ばれます。 - コンパレーター

入力電圧を参照電圧と比較して大小を判定する回路です。 - 毎秒56ギガビット(56Gbps)

今回の開発では、イーサネットの次世代技術である400ギガビットイーサ(GbE)で用いられるトランシーバーを想定し、56Gbpsのトランシーバーを試作しました。 - 発表論文の情報

F. Tachibana et al., “A 56-Gb/s PAM4 Transceiver with False-Lock-Aware Locking Scheme for Mueller-Müller CDR,” IEEE

European Solid-state Circuits Conference 2022 (ESSCIRC 2022) - デイジーチェーン技術

メモリコントローラーとNANDフラッシュメモリの間を高速シリアル通信で数珠つなぎに接続する方法で、バス接続と比べて広帯域化、大容量化に有利な方法です。 - Mobile Edge Computing(MEC)サーバー

5Gなどにおいて端末に近い場所に設置されるサーバーのことで、主に低遅延特性を実現するために用いられます。

※記載されている社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。

- 本資料に掲載されている情報(製品の仕様、サービスの内容およびお問い合わせ先など)は、発表日現在の情報です。予告なしに変更されることがありますので、あらかじめご了承ください。